# Low EMI, Spread Modulating, Clock Generator

#### Features:

- ICS91720 is a Spread Spectrum Clock targeted for Mobile PC and LCD panel applications that generates an EMI-optimized clock signal (EMI peak reduction of 7-14 dB on 3rd-19th harmonics) through use of Spread Spectrum techniques.

- ICS91720 focuses on the lower input frequency range of 14.318 to 80.00 MHz with a spread modulation of 20kHz to 40kHz.

#### **Specifications:**

- Supply Voltages: V<sub>DD</sub> = 3.3V ±0.3V

- Frequency range: 14.318 MHz ≤Fin ≥ 80 MHz

- Cyc to Cyc jitter: <150ps</li>Output duty cycle 45-55%

- Guarantees +85°C operational condition.

- 8-pin SOIC/TSSOP

- · Reference input

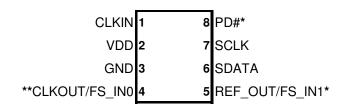

### Pin Configuration

#### 8 Pin SOIC/TSSOP

- \* Internal Pull-Up Resistor

- \*\* Internal Pull-Down Resistor

#### **Functionality**

| FSIN_1 | FSIN <sub>0</sub> | MHz                       | Spread % default  |

|--------|-------------------|---------------------------|-------------------|

| 0      | 0                 | 14.318 MHz in> 27MHz out  | -0.8 down spread  |

| 0      | 1                 | 14.318MHz>14.318MHz out   | -1.00 down spread |

| 1      | 0                 | 27.00MHz in> 27.00MHz out | -1.25 down spread |

| 1      | 1                 | 48.00MHz in>48.00 MHz out | -0.8 down spread  |

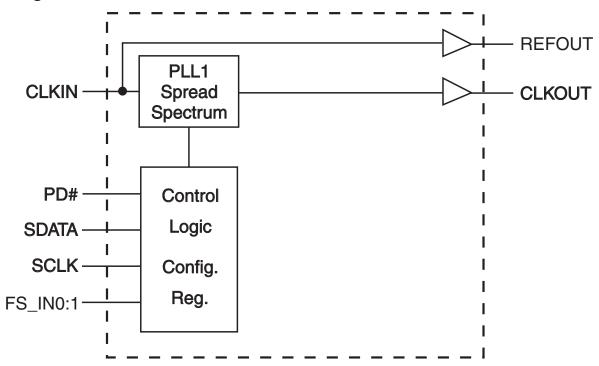

### **Block Diagram**

# Pin Description

| PIN# | PIN NAME                                | PIN TYPE | DESCRIPTION                                                                                                                                                                                                                     |

|------|-----------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CLKIN                                   | POWER    | Input for reference clock.                                                                                                                                                                                                      |

| 2    | VDD                                     | INPUT    | Power supply, nominal 3.3V                                                                                                                                                                                                      |

| 3    | GND                                     | POWER    | Ground pin.                                                                                                                                                                                                                     |

| 4    | *************************************** |          | Modulated clock output.                                                                                                                                                                                                         |

| 4    | **CLKOUT/FS_IN0                         | I/O      | Frequency select latch input. Refer to the functionality table.                                                                                                                                                                 |

| 5    | DEE OUT/ES IN4*                         |          | Un-modulated 3.3V reference clock output.                                                                                                                                                                                       |

| 3    | REF_OUT/FS_IN1*                         | I/O      | Frequency select latch input. Refer to the functionality table.                                                                                                                                                                 |

| 6    | SDATA                                   | POWER    | Data pin for I2C circuitry 5V tolerant                                                                                                                                                                                          |

| 7    | SCLK                                    | POWER    | Clock pin of I2C circuitry 5V tolerant                                                                                                                                                                                          |

| 8    | PD#*                                    | POWER    | Asynchronous active low input pin used to power down the device into a low power state. The internal clocks are disabled and the VCO and the crystal are stopped. The latency of the power down will not be greater than 1.8ms. |

<sup>\*</sup> Internal Pull-Up Resistor \*\* Internal Pull-Down Resistor

**Table 1: Frequency Configuration Table** (See I2C Byte 0)

|              | FS4 | FS3 | FS2 | FS1 | FS0 | Sprd Type  | Sprd % |

|--------------|-----|-----|-----|-----|-----|------------|--------|

|              | 0   | 0   | 0   | 0   | 0   |            | 0.60   |

|              | 0   | 0   | 0   | 0   | 1   | DOWN       | 0.80   |

|              | 0   | 0   | 0   | 1   | 0   | SPREAD     | 1.00   |

| 14in/27out   | 0   | 0   | 0   | 1   | 1   | (-)        | 1.25   |

| 14111/27 Out | 0   | 0   | 1   | 0   | 0   | ( )        | 1.50   |

|              | 0   | 0   | 1   | 0   | 1   |            | 2.00   |

|              | 0   | 0   | 1   | 1   | 0   | CENTER SPD | 0.50   |

|              | 0   | 0   | 1   | 1   | 1   | (+/-)      | 1.00   |

|              | 0   | 1   | 0   | 0   | 0   | DOWN       | 0.60   |

|              | 0   | 1   | 0   | 0   | 1   | SPREAD     | 1.00   |

|              | 0   | 1   | 0   | 1   | 0   |            | -0.80  |

|              | 0   | 1   | 0   | 1   | 1   |            | +/-0.3 |

|              | 0   | 1   | 1   | 0   | 0   |            | 1.50   |

|              | 0   | 1   | 1   | 0   | 1   | DOWN       | 1.75   |

|              | 0   | 1   | 1   | 1   | 0   | SPREAD     | 2.00   |

| 14in/14out   | 0   | 1   | 1   | 1   | 1   | (-)        | 2.50   |

| 27in/27out   | 1   | 0   | 0   | 0   | 0   | ( )        | 3.00   |

|              | 1   | 0   | 0   | 0   | 1   |            | -1.25  |

|              | 1   | 0   | 0   | 1   | 0   |            | 0.40   |

|              | 1   | 0   | 0   | 1   | 1   | CENTER     | 0.50   |

|              | 1   | 0   | 1   | 0   | 0   | SPREAD     | 0.70   |

|              | 1   | 0   | 1   | 0   | 1   | (+/-)      | 1.00   |

|              | 1   | 0   | 1   | 1   | 0   | (17)       | 1.20   |

|              | 1   | 0   | 1   | 1   | 1   |            | 1.50   |

|              | 1   | 1   | 0   | 0   | 0   |            | 0.60   |

|              | 1   | 1   | 0   | 0   | 1   | DOWN       | 0.80   |

|              | 1   | 1   | 0   | 1   | 0   | SPREAD     | 1.00   |

| 48in/48out   | 1   | 1   | 0   | 1   | 1   | (-)        | 1.25   |

| 66in/66out   | 1   | 1   | 1   | 0   | 0   | ( )        | 1.50   |

|              | 1   | 1   | 1   | 0   | 1   |            | 2.00   |

|              | 1   | 1   | 1   | 1   | 0   | CENTER SPD | 0.50   |

|              | 1   | 1   | 1   | 1   | 1   | (+/-)      | 1.00   |

Above is the hard coded 5 bit (32 entry) ROM table. FS2:0 are ONLY accessible through I2C software programming bits (byte0 bits5:7). FS3 and FS4 can also be decoded from FS\_IN0:1 latched input hardware pins.

FS2 = 0, FS1 = 0, FS0 = 1 upon power-up (refer to the functionality table on page 1). To access non-default spread entries in the ROM, byte0 programming should be used. In order to change the power up default of FS\_IN1:0 = 10 (-1.25% down spread) to any other spread % entry, first change byte0bit 0 to software selection by switching this bit to a '1' and then program the desired percentage by changing byte0 bits 7:3.

FS\_IN0 →FS3 and FS\_IN1 →FS4. Upon power-up the default is to use hardware selections of FS\_IN0:1 latched values.

# General I<sup>2</sup>C serial interface information

#### **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address D4 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X -1 (see Note 2)

- ICS clock will acknowledge each byte one at a time

- · Controller (host) sends a Stop bit

| Ind   | ex Block W                  | /rit   | e Operation          |  |  |  |

|-------|-----------------------------|--------|----------------------|--|--|--|

| Cor   | ntroller (Host)             |        | ICS (Slave/Receiver) |  |  |  |

| Т     | starT bit                   |        |                      |  |  |  |

| Slav  | e Address D4 <sub>(H)</sub> |        |                      |  |  |  |

| WR    | WRite                       |        |                      |  |  |  |

|       |                             | ACK    |                      |  |  |  |

| Begi  | nning Byte = N              |        |                      |  |  |  |

|       |                             |        | ACK                  |  |  |  |

| Data  | Byte Count = X              |        |                      |  |  |  |

|       |                             |        | ACK                  |  |  |  |

| Begir | ning Byte N                 |        |                      |  |  |  |

|       |                             |        | ACK                  |  |  |  |

|       | 0                           | ţ      |                      |  |  |  |

|       | 0                           | X Byte | 0                    |  |  |  |

|       | 0                           | ×      | 0                    |  |  |  |

|       |                             |        | 0                    |  |  |  |

| Byte  | e N + X - 1                 |        |                      |  |  |  |

|       | -                           |        | ACK                  |  |  |  |

| Р     | stoP bit                    |        |                      |  |  |  |

#### How to Read:

- · Controller (host) will send start bit.

- Controller (host) sends the write address D4 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address D5  $_{\scriptscriptstyle (H)}$

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- · Controller (host) will need to acknowledge each byte

- · Controllor (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| Ind   | Operation                 |                     |                    |  |

|-------|---------------------------|---------------------|--------------------|--|

| Con   | troller (Host)            | IC                  | S (Slave/Receiver) |  |

| Т     | starT bit                 |                     |                    |  |

| Slave | Address D4 <sub>(H)</sub> |                     |                    |  |

| WR    | WRite                     |                     |                    |  |

|       |                           |                     | ACK                |  |

| Begir | nning Byte = N            |                     |                    |  |

|       |                           |                     | ACK                |  |

| RT    | Repeat starT              |                     |                    |  |

| Slave | Address D5 <sub>(H)</sub> |                     |                    |  |

| RD    | ReaD                      |                     |                    |  |

|       |                           |                     | ACK                |  |

|       |                           |                     |                    |  |

|       |                           | Data Byte Count = X |                    |  |

|       | ACK                       |                     |                    |  |

|       |                           |                     | Beginning Byte N   |  |

|       | ACK                       |                     |                    |  |

|       |                           | ţ                   | 0                  |  |

|       | 0                         | X Byte              | 0                  |  |

|       | 0                         | ×                   | 0                  |  |

| . 0   |                           |                     |                    |  |

|       |                           |                     | Byte N + X - 1     |  |

| N     | Not acknowledge           |                     |                    |  |

| Р     | stoP bit                  |                     |                    |  |

0698D—10/05/04

| Byte  |      | Affected      | Pin                     |      | Bit C                                                 |           |     |

|-------|------|---------------|-------------------------|------|-------------------------------------------------------|-----------|-----|

| 0     | Pin# | Name          | Control Function        | Type | 0                                                     | 1         | PWD |

| Bit 7 | -    | FS0           | Spread/FS0              | RW   | Carood a                                              | oroontogo | 1   |

| Bit 6 | -    | FS1           | Spread/FS1              | RW   | Spread percentage See Table 1 These are I2C bits only |           | 0   |

| Bit 5 |      | FS2           | Spread/FS2              | RW   |                                                       |           | 0   |

| Bit 4 |      | FS3           | Spread/FS3              | RW   |                                                       |           | 0   |

| Bit 3 |      | FS4           | FS4                     | RW   | OI                                                    | пу        | 0   |

| Bit 2 |      | PD# Tri_Sate  | PD# Tri_Sate            | RW   | Hi-Z                                                  | LOW       | 1   |

| Bit 1 |      | Spread Enable | Spread Enable           | RW   | OFF                                                   | ON        | 1   |

|       |      |               | Spread Spectrum Control |      |                                                       |           |     |

|       |      |               | FS 3:4 Hard/Software    |      |                                                       |           |     |

| Bit 0 |      | HW/SW Control | Select                  | RW   | HW                                                    | SW        | 0   |

| Byte  |      | Affected   | Pin               |      | Bit Co  | ontrol |     |

|-------|------|------------|-------------------|------|---------|--------|-----|

| 1     | Pin# | Name       | Control Function  | Type | 0       | 1      | PWD |

| Bit 7 |      | REF_OUT    | REF_OUT_Enable    | RW   | Disable | Enable | 1   |

| Bit 6 | -    | REF_OUT    | Slew Rate REF-OUT | RW   | Nominal | Fast   | 1   |

| Bit 5 |      | FS-IN_1    | FS-IN_1 Readback  | R    | -       | 1      | Χ   |

| Bit 4 |      | FS-IN_0    | FS-IN_0 Readback  | R    | -       | 1      | Χ   |

| Bit 3 |      | CLK_OUT    | Slew Rate CLK-OUT | RW   | Nominal | Fast   | 1   |

| Bit 2 |      | CLK_OUT    | CLK_OUT_Enable    | RW   | Disable | Enable | 1   |

| Bit 1 |      | (Reserved) | (Reserved)        | R    | -       | -      | 1   |

| Bit 0 |      | (Reserved) | (Reserved)        | R    | -       | ı      | 1   |

| Byte  |       | Affected   | Pin              |      | Bit C | ontrol |     |

|-------|-------|------------|------------------|------|-------|--------|-----|

| 2     | Pin # | Name       | Control Function | Type | 0     | 1      | PWD |

| Bit 7 | Х     | -          | (Reserved)       | -    | ı     | -      | 1   |

| Bit 6 | Х     | (Reserved) | (Reserved)       | RW   | ı     | -      | 1   |

| Bit 5 | Х     | (Reserved) | (Reserved)       | RW   | ı     | -      | 1   |

| Bit 4 | Х     | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 3 | Х     | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 2 | Х     | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 1 | Х     | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 0 | Х     | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Byte  |      | Affected   | Pin              |      | Bit C | ontrol |     |

|-------|------|------------|------------------|------|-------|--------|-----|

| 3     | Pin# | Name       | Control Function | Туре | 0     | 1      | PWD |

| Bit 7 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 6 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 5 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 4 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 3 | Х    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 2 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 1 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 0 | X    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Byte  |      | Affected   | Pin              |      | Bit C | ontrol |     |

|-------|------|------------|------------------|------|-------|--------|-----|

| 4     | Pin# | Name       | Control Function | Type | 0     | 1      | PWD |

| Bit 7 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 6 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 5 | Χ    | (Reserved) | (Reserved)       | RW   | •     | -      | 1   |

| Bit 4 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 3 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 2 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 1 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 0 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Byte  |      | Affected   | Pin              |      | Bit C | ontrol |     |

|-------|------|------------|------------------|------|-------|--------|-----|

| 5     | Pin# | Name       | Control Function | Type | 0     | 1      | PWD |

| Bit 7 | Χ    | (Reserved) | (Reserved)       | -    | -     | -      | 1   |

| Bit 6 | Χ    | (Reserved) | (Reserved)       | -    | -     | -      | 1   |

| Bit 5 | Χ    | (Reserved) | (Reserved)       | -    | -     | -      | 1   |

| Bit 4 | Χ    | (Reserved) | (Reserved)       | -    | -     | -      | 1   |

| Bit 3 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 2 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 1 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Bit 0 | Χ    | (Reserved) | (Reserved)       | RW   | -     | -      | 1   |

| Byte  |      | Affected          | Pin              |      | Bit C | ontrol |     |

|-------|------|-------------------|------------------|------|-------|--------|-----|

| 6     | Pin# | Name              | Control Function | Type | 0     | 1      | PWD |

| Bit 7 | Χ    | Revision ID Bit 3 | (Reserved)       | R    | -     | -      | 1   |

| Bit 6 | Χ    | Revision ID Bit 2 | (Reserved)       | R    | -     | -      | 1   |

| Bit 5 | Χ    | Revision ID Bit 1 | (Reserved)       | R    | -     | -      | 1   |

| Bit 4 | Χ    | Revision ID Bit 0 | (Reserved)       | R    | -     | -      | 1   |

| Bit 3 | Χ    | Vendor ID Bit 3   | (Reserved)       | R    | -     | -      | 1   |

| Bit 2 | Χ    | Vendor ID Bit 2   | (Reserved)       | R    | -     | -      | 1   |

| Bit 1 | Χ    | Vendor ID Bit 1   | (Reserved)       | R    | -     | -      | 1   |

| Bit 0 | Χ    | Vendor ID Bit 0   | (Reserved)       | R    | -     | -      | 1   |

## **Absolute Maximum Ratings**

Supply Voltage..... 3.7 V

Power Dissipation . . . . . . . . . . . . 0.5 W

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 85$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                                        | SYMBOL               | CONDITIONS                                                | MIN                   | TYP | MAX            | UNITS |

|--------------------------------------------------|----------------------|-----------------------------------------------------------|-----------------------|-----|----------------|-------|

| Input High Voltage                               | $V_{IH}$             |                                                           | 2                     |     | $V_{DD} + 0.3$ | V     |

| Input Low Voltage                                | $V_{IL}$             |                                                           | V <sub>SS</sub> - 0.3 |     | 0.8            | V     |

| Input High Current                               | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                         | -5                    |     | 5              | mA    |

| Input Low Current                                | $I_{\rm IL1}$        | $V_{IN} = 0 \text{ V}$ ; Inputs with no pull-up resistors | -5                    |     |                | mA    |

| Powerdown Current                                | I <sub>DD3.3PD</sub> |                                                           |                       | 3   | 5              | mA    |

| Input Frequency                                  | Fi                   | $V_{DD} = 3.3 \text{ V}$                                  | 14.318                | ì   | 80             | MHz   |

| Pin Inductance                                   | Lpin                 |                                                           |                       |     | 7              | nΗ    |

|                                                  | C <sub>IN</sub>      | Logic Inputs                                              |                       |     | 5              | рF    |

| Input Capacitance <sup>1</sup>                   | $C_OUT$              | Output pin capacitance                                    |                       |     | 6              | рF    |

|                                                  | $C_{INX}$            | X1 & X2 pins                                              | 27                    | 36  | 45             | рF    |

| Transition time <sup>1</sup>                     | T <sub>trans</sub>   | To 1st crossing of target frequency                       |                       |     | 3              | ms    |

| Settling time <sup>1</sup> Ts                    |                      | From 1st crossing to 1% target frequency                  |                       |     | 3              | ms    |

| Clk Stabilization <sup>1</sup> T <sub>STAB</sub> |                      | From $V_{DD} = 3.3 \text{ V}$ to 1% target frequency      |                       |     | 3              | ms    |

| Delay <sup>1</sup>                               | $t_{PZH}, t_{PZL}$   | Output enable delay (all outputs)                         | 1                     |     | 10             | ns    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - CLKOUT**

$T_A = 0 - 85 \,^{\circ}\text{C}$ ;  $V_{DD} = 3.3 \text{V} + -5\%$ ;  $C_L = 10\text{-}20 \,^{\circ}\text{pF}$  (unless otherwise specified)

| PARAMETER              | SYMBOL                  | CONDITIONS                                              | MIN | TYP | MAX | UNITS |

|------------------------|-------------------------|---------------------------------------------------------|-----|-----|-----|-------|

| Output High Voltage    | $V_{OH3}$               | $I_{OH} = -1 \text{ mA}$                                | 2.4 |     |     | V     |

| Output Low Voltage     | $V_{OL3}$               | $I_{OL} = 1 \text{ mA}$                                 |     |     | 0.4 |       |

| Rise Time              | tr3                     | $V_{OL} = 0.41V, V_{OH} = 0.86V$                        | 0.5 | 0.6 | 1   | ns    |

| Fall Time              | tf3                     | $V_{OH} = 0.86V V_{OL} = 0.41V$                         | 0.5 | 0.6 | 1   | ns    |

| Duty Cycle             | d <sub>t3</sub>         | measurement from differential wavefrom - 0.35V to +035V | 45  | 50  | 55  | %     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> 1 | $V_T = 50\%$                                            |     | 50  | 150 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - REF**

$T_A = 0 - 85 \,^{\circ}\text{C}$ ;  $V_{DD} = 3.3 V$  +/-5%;  $C_L = 10\text{-}20 \; \text{pF}$  (unless otherwise specified)

| PARAMETER           | SYMBOL                         | CONDITIONS                                                  | MIN | TYP | MAX | UNITS |

|---------------------|--------------------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| Output Frequency    | F <sub>O1</sub>                |                                                             |     |     |     | MHz   |

| Output Impedance    | R <sub>DSP1</sub> <sup>1</sup> | $V_{O} = V_{DD}^{*}(0.5)$                                   | 20  | 48  | 60  | Ω     |

| Output High Voltage | $V_{OH}^{-1}$                  | $I_{OH} = -1 \text{ mA}$                                    | 2.4 |     |     | V     |

| Output Low Voltage  | $V_{OL}^{1}$                   | $I_{OL} = 1 \text{ mA}$                                     |     |     | 0.4 | V     |

| Output High Current | l <sub>OH</sub> <sup>1</sup>   | $V_{OH@MIN} = 1.0 \text{ V}, V_{OH@MAX} = 3.135 \text{ V}$  | -29 |     | -23 | mA    |

| Output Low Current  | $I_{OL}^{1}$                   | $V_{OL @MIN} = 1.95 \text{ V}, V_{OL @MAX} = 0.4 \text{ V}$ | 29  |     | 27  | mA    |

| Rise Time           | $t_{r1}^1$                     | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$            | 1   | 1.2 | 2   | ns    |

| Fall Time           | t <sub>f1</sub> 1              | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$            | 1   | 1.2 | 2   | ns    |

| Duty Cycle          | $d_{t1}^{-1}$                  | $V_T = 1.5 \text{ V}$                                       | 45  | 51  | 55  | %     |

| Jitter              | t <sub>jcyc-cyc</sub> 1        | $V_T = 1.5 \text{ V}$                                       |     | 105 | 300 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

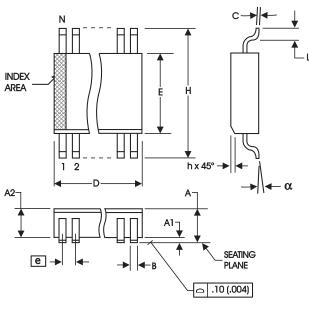

8-pin SOIC

150 mil (Narrow Body) SOIC

| ioo iiii (ilaiion 20a), oolo |                        |           |                   |          |  |  |

|------------------------------|------------------------|-----------|-------------------|----------|--|--|

|                              | In Milli               | meters    | In Inches         |          |  |  |

| SYMBOL                       | COMMON D               | IMENSIONS | COMMON DIMENSIONS |          |  |  |

|                              | MIN                    | MAX       | MIN               | MAX      |  |  |

| Α                            | 1.35                   | 1.75      | .0532             | .0688    |  |  |

| A1                           | 0.10                   | 0.25      | .0040             | .0098    |  |  |

| В                            | 0.33                   | 0.51      | .013              | .020     |  |  |

| С                            | 0.19                   | 0.25      | .0075             | .0098    |  |  |

| D                            | SEE VARIATIONS         |           | SEE VARIATIONS    |          |  |  |

| E                            | 3.80                   | 4.00      | .1497             | .1574    |  |  |

| е                            | 1.27 BASIC 0.050 BASIC |           | BASIC             |          |  |  |

| Н                            | 5.80                   | 6.20      | .2284             | .2440    |  |  |

| h                            | 0.25                   | 0.50      | .010              | .020     |  |  |

| L                            | 0.40                   | 1.27      | .016              | .050     |  |  |

| N                            | SEE VARIATIONS         |           | SEE VAF           | RIATIONS |  |  |

| α                            | 0°                     | 8°        | 0°                | 8°       |  |  |

#### **VARIATIONS**

|  | N | Dr   | nm.  | D (inch) |       |  |

|--|---|------|------|----------|-------|--|

|  |   | MIN  | MAX  | MIN      | MAX   |  |

|  | 8 | 4.80 | 5.00 | .1890    | .1968 |  |

Reference Doc.: JEDEC Publication 95, MS-012

10-0030

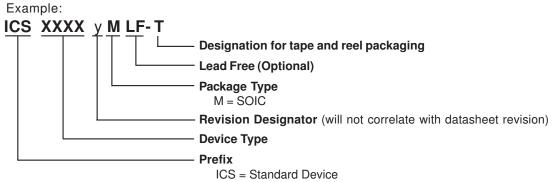

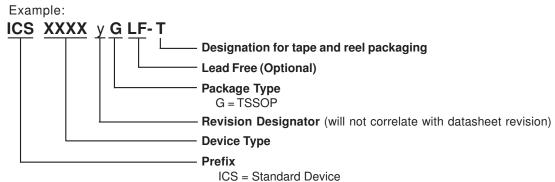

# **Ordering Information**

ICS91720yMLF-T

0698D—10/05/04

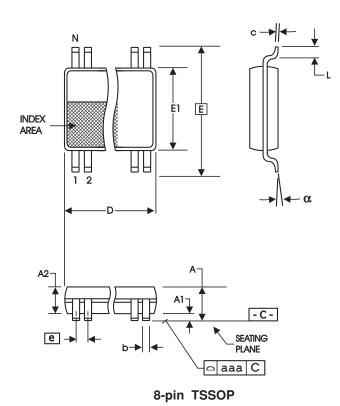

4.40 mm. Body, 0.65 mm. Pitch TSSOP (173 mil) (25.6 mil)

|        | In Millimeters   |           | In Inches         |          |  |

|--------|------------------|-----------|-------------------|----------|--|

| SYMBOL | COMMON D         | IMENSIONS | COMMON DIMENSIONS |          |  |

|        | MIN              | MAX       | MIN               | MAX      |  |

| Α      |                  | 1.20      |                   | .047     |  |

| A1     | 0.05             | 0.15      | .002              | .006     |  |

| A2     | 0.80             | 1.05      | .032              | .041     |  |

| b      | 0.19             | 0.30      | .007              | .012     |  |

| С      | 0.09             | 0.20      | .0035             | .008     |  |

| D      | SEE VAR          | RIATIONS  | SEE VAF           | RIATIONS |  |

| E      | 6.40 E           | BASIC     | 0.252 BASIC       |          |  |

| E1     | 4.30             | 4.50      | .169              | .177     |  |

| е      | e 0.65 BASIC 0.0 |           | 0.0256            | BASIC    |  |

| L      | 0.45             | 0.75      | .018              | .030     |  |

| N      | SEE VARIATIONS   |           | SEE VAF           | RIATIONS |  |

| α      | 0°               | 8°        | 0°                | 8°       |  |

| aaa    | -                | 0.10      |                   | .004     |  |

#### **VARIATIONS**

|  | N | D mm. |      | D (inch) |      |

|--|---|-------|------|----------|------|

|  |   | MIN   | MAX  | MIN      | MAX  |

|  | 8 | 2.90  | 3.10 | .114     | .122 |

Reference Doc.: JEDEC Publication 95, MO-153

10-0035

# **Ordering Information**

ICS91720yGLF-T

0698D—10/05/04