# National Semiconductor

## LM6125/LM6225/LM6325 High Speed Buffer

## **General Description**

The LM6125 family of high speed unity gain buffers slew at 800 V/µs and have a small signal bandwidth of 50 MHz while driving a 50 $\Omega$  load. These buffers drive ±300 mA peak and do not oscillate while driving large capacitive loads. The LM6125 contains unique features not found in power buffers; these include current limit, thermal shutdown, electronic shutdown, and an error flag that warns of fault conditions.

These buffers are built with National's VIP<sup>™</sup> (Vertically Integrated PNP) process which provides fast PNP transistors that are true complements to the already fast NPN devices. This advanced junction-isolated process delivers high speed performance without the need for complex and expensive dielectric isolation.

#### Features

■ High slew rate: 800 V/µs

- Stable with large capacitive loads

- Current and thermal limiting

- Electronic shutdown

- 5V to ±15V operation guaranteed

- Fully specified to drive 50Ω lines

#### **Applications**

- Line Driving

- Radar

- Sonar

LM6125/LM6225/LM6325 High Speed Buffer

December 1994

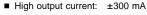

## Simplified Schematic and Block Diagram 2 V+ THERMAL SHUTDOWN FI AG FAULT 5 03 DETEC 20 CURRENT LIMIT 3 ۷оот ELECTRONIC 6 7 SHUTDOWN (9) (8) DS009 4 V-(2) DS009222-2 Numbers in () are for 14-pin N DIP. VIP™ is a trademark of National Semiconductor Corporation. DS009222 © 1999 National Semiconductor Corporation www.national.com

www.national.com

## Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage                              | 36V (±18V)                   |

|---------------------------------------------|------------------------------|

| Input to Output Voltage (Note 2)            | ±7V                          |

| Input Voltage                               | ±Vsupply                     |

| Output Short-Circuit to GND                 |                              |

| (Note 3)                                    | Continuous                   |

| Flag Output Voltage                         | $GND \le Vflag \le +Vsupply$ |

| Storage Temperature Range                   | -65°C to +150°C              |

| Lead Temperature<br>(Soldering, 10 seconds) | 260°C                        |

| ESD Tolerance (Note 9)         | ±1500V          |

|--------------------------------|-----------------|

| $\theta_{JA}$ (Note 4)         |                 |

| H Package                      | 150°C/W         |

| N Package                      | 40°C/W          |

| Maximum Junction               |                 |

| Temperature (T <sub>J</sub> )  | 150°C           |

| Operating Temperature Range    |                 |

| LM6125                         | –55°C to +125°C |

| LM6225                         | -40°C to +85°C  |

| LM6325                         | 0°C to +70°C    |

| Operating Supply Voltage Range | 4.75V to ±16V   |

|                                |                 |

## **DC Electrical Characteristics**

The following specifications apply for Supply Voltage =  $\pm 15V$ ,  $V_{CM} = 0$ ,  $R_L \ge 100 \text{ k}\Omega$  and  $R_S = 50\Omega$  unless otherwise noted. **Boldface** limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol           | Parameter          | Conditions                                                 | Тур   | LM6125        | LM6225   | LM6325   | Unit     |

|------------------|--------------------|------------------------------------------------------------|-------|---------------|----------|----------|----------|

|                  |                    |                                                            |       | Limit         | Limit    | Limit    |          |

|                  |                    |                                                            |       | (Notes 5, 10) | (Note 5) | (Note 5) |          |

| A <sub>V1</sub>  | Voltage Gain 1     | $R_L = 1k\Omega$ , $V_{IN} = \pm 10V$                      | 0.990 | 0.980         | 0.980    | 0.970    |          |

|                  |                    |                                                            |       | 0.970         | 0.950    | 0.950    |          |

| A <sub>V2</sub>  | Voltage Gain 2     | $R_{L} = 50\Omega, V_{IN} = \pm 10V$                       | 0.900 | 0.860         | 0.860    | 0.850    | \<br>V/\ |

|                  |                    |                                                            |       | 0.800         | 0.820    | 0.820    | Mi       |

| A <sub>V3</sub>  | Voltage Gain 3     | $R_{L} = 50\Omega, V + = 5V$                               | 0.840 | 0.780         | 0.780    | 0.750    |          |

|                  | (Note 6)           | V <sub>IN</sub> = 2 V <sub>PP</sub> (1.5 V <sub>PP</sub> ) |       | 0.750         | 0.700    | 0.700    |          |

| Vos              | Offset Voltage     | $R_L = 1 k\Omega$                                          | 15    | 30            | 30       | 50       | m        |

|                  |                    |                                                            |       | 50            | 60       | 100      | Ma       |

| Iв               | Input Bias Current | R <sub>L</sub> = 1 kΩ, R <sub>S</sub> = 10 kΩ              | 1     | 4             | 4        | 5        | μA       |

|                  |                    |                                                            |       | 7             | 7        | 7        | Ma       |

| R <sub>IN</sub>  | Input Resistance   | R <sub>L</sub> = 50Ω                                       | 5     |               |          |          | M        |

| CIN              | Input Capacitance  |                                                            | 3.5   |               |          |          | pl       |

| Ro               | Output Resistance  | $I_{OUT} = \pm 10 \text{ mA}$                              | 3     | 5             | 5        | 5        | 0        |

|                  |                    |                                                            |       | 10            | 10       | 6        | Ma       |

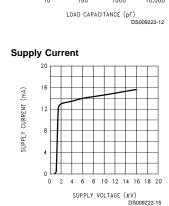

| I <sub>S1</sub>  | Supply Current 1   | R <sub>L</sub> = ∞                                         | 15    | 18            | 18       | 20       |          |

|                  |                    |                                                            |       | 20            | 20       | 22       |          |

| I <sub>S2</sub>  | Supply Current 2   | R <sub>L</sub> = ∞, V+ = 5V                                | 14    | 16            | 16       | 18       | m        |

|                  |                    |                                                            |       | 18            | 18       | 20       | Ma       |

| I <sub>S/D</sub> | Supply Current     | $R_1 = \infty$ , $V \pm = \pm 15V$                         | 1.1   | 1.5           | 1.5      | 1.5      |          |

|                  | in Shutdown        |                                                            |       | 2.0           | 2.0      | 2.0      |          |

| V <sub>O1</sub>  | Output Swing 1     | $R_{L} = 1 k\Omega$                                        | 13.5  | 13.3          | 13.3     | 13.2     |          |

|                  |                    |                                                            |       | 13            | 13       | 13       |          |

| V <sub>O2</sub>  | Output Swing 2     | $R_1 = 100\Omega$                                          | 12.7  | 11.5          | 11.5     | 11       |          |

|                  |                    |                                                            |       | 10            | 10       | 10       | Mi       |

| V <sub>O3</sub>  | Output Swing 3     | $R_1 = 50\Omega$                                           | 12    | 11            | 11       | 10       |          |

|                  |                    |                                                            |       | 9             | 9        | 9        |          |

| V <sub>O4</sub>  | Output Swing 4     | $R_1 = 50\Omega$                                           | 1.8   | 1.6           | 1.6      | 1.6      | V        |

|                  |                    |                                                            |       | 1.3           | 1.4      | 1.5      | M        |

| PSRR             | Power Supply       | V+ = 5V (Note 6)                                           | 70    | 60            | 60       | 60       | d        |

|                  | Rejection Ratio    |                                                            |       | 55            | 50       | 50       | Mi       |

| V <sub>OL</sub>  | Flag Pin Output    | $V \pm = \pm 5V$ to $\pm 15V$                              | 1     | 300           | 300      | 340      | m        |

|                  | Low Voltage        | $V_{S/D} = 0V$                                             |       | 400           | 400      | 400      | Ma       |

www.national.com

| DC Electrical | Characteristics | (Continued) |

|---------------|-----------------|-------------|

|---------------|-----------------|-------------|

•

The following specifications apply for Supply Voltage = ±15V,  $V_{CM}$  = 0,  $R_L \ge 100 \text{ k}\Omega$  and  $R_S$  = 50 $\Omega$  unless otherwise noted. Boldface limits apply for  $T_A = T_{LI} = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_{LI} = 25^{\circ}C$ .

| Symbol          | vmbol Parameter Conditions Typ LM6125 | Conditions                      | Тур   | LM6125        | LM6225   | LM6325   | Units |

|-----------------|---------------------------------------|---------------------------------|-------|---------------|----------|----------|-------|

|                 |                                       | Limit                           | Limit | 1             |          |          |       |

|                 |                                       |                                 |       | (Notes 5, 10) | (Note 5) | (Note 5) |       |

| I <sub>он</sub> | Flag Pin Output                       | V <sub>он</sub> Flag Pin = 15V  | 0.01  | 10            | 10       | 10       | μA    |

|                 | High Current                          | (Note 6)                        |       | 20            | 20       | 20       | Max   |

| V <sub>TH</sub> | Shutdown Threshold                    |                                 | 1.4   |               |          |          | V     |

| VIH             | Shutdown Pin                          |                                 |       | 2.0           | 2.0      | 2.0      | V     |

|                 | Trip Point High                       |                                 |       | 2.0           | 2.0      | 2.0      | Min   |

| VIL             | Shutdown Pin                          |                                 |       | 0.8           | 0.8      | 0.8      | V     |

|                 | Trip Point Low                        |                                 |       | 0.8           | 0.8      | 0.8      | Max   |

| I <sub>IL</sub> | Shutdown Pin                          | $V_{S/D} = 0V$                  | -0.07 | -10           | -10      | -10      | μA    |

|                 | Input Low Current                     |                                 |       | -20           | -20      | -20      | Max   |

| IIH             | Shutdown Pin                          | $V_{S/D} = 5V$                  | -0.05 | -10           | -10      | -10      | μA    |

|                 | Input High Current                    |                                 |       | -20           | -20      | -20      | Max   |

| Io              | Bi-State Output                       | Shutdown Pin = 0V               | 1     | 50            | 50       | 100      | μA    |

|                 | Current                               | $V_{OUT} = +5V \text{ or } -5V$ |       | 2000          | 100      | 200      |       |

## **AC Electrical Characteristics**

The following specifications apply for Supply Voltage =  $\pm 15V$ ,  $V_{CM} = 0$ ,  $R_L \ge 100 \text{ k}\Omega$  and  $R_S = 50\Omega$  unless otherwise noted. **Boldface** limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol                          | Parameter                                                     | Conditions                                                                           | Тур  | LM6125   | LM6225   | LM6325   | Units      |

|---------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------|------|----------|----------|----------|------------|

|                                 |                                                               |                                                                                      |      | Limit    | Limit    | Limit    | 1          |

|                                 |                                                               |                                                                                      |      | (Note 5) | (Note 5) | (Note 5) |            |

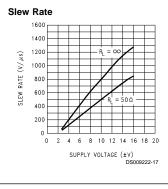

| SR <sub>1</sub>                 | Slew Rate 1                                                   | $V_{IN} = \pm 11V, R_L = 1 k\Omega$                                                  | 1200 |          |          |          | V/µs       |

| SR <sub>2</sub>                 | Slew Rate 2                                                   | $V_{IN} = \pm 11V, R_L = 50\Omega$<br>(Note 8)                                       | 800  | 550      | 550      | 550      | Min        |

| $SR_3$                          | Slew Rate 3                                                   | $V_{IN} = 2 V_{PP}, R_{L} = 50\Omega$ $V_{+} = 5V \text{ (Note 6)}$                  | 50   |          |          |          | 1          |

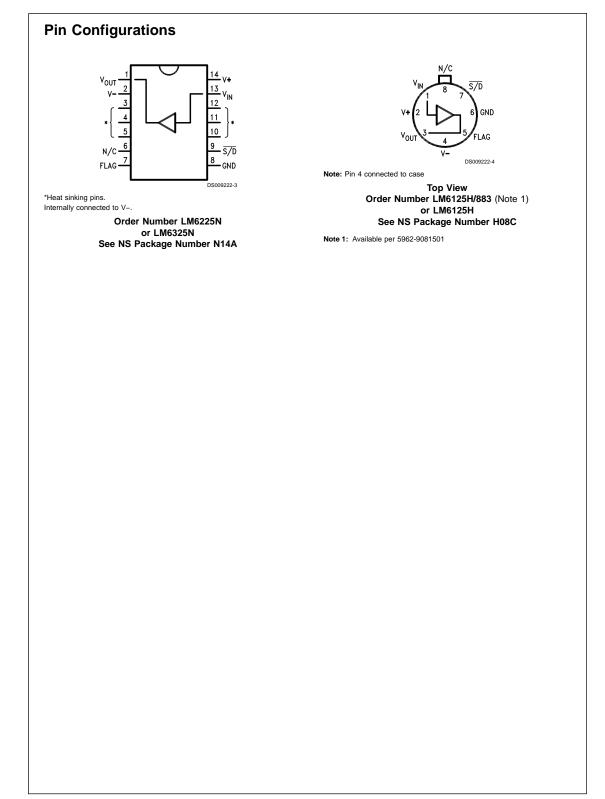

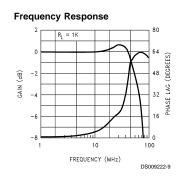

| BW                              | -3 dB Bandwidth                                               | $V_{IN} = 100 \text{ mV}_{PP}$<br>$R_L = 50\Omega, C_L \le 10 \text{ pF}$            | 50   | 30       | 30       | 30       | MHz<br>Min |

| t <sub>r</sub> , t <sub>f</sub> | Rise Time<br>Fall Time                                        | $R_{L} = 50\Omega, C_{L} \le 10 \text{ pF}$ $V_{O} = 100 \text{ mV}_{PP}$            | 8.0  |          |          |          | ns         |

| t <sub>PD</sub>                 | Propagation<br>Delay Time                                     | $R_{L} = 50\Omega, C_{L} \le 10 \text{ pF}$<br>V <sub>O</sub> = 100 mV <sub>PP</sub> | 4.0  |          |          |          | ns         |

| O <sub>S</sub>                  | Overshoot                                                     | $R_{L} = 50\Omega, C_{L} \le 10 \text{ pF}$ $V_{O} = 100 \text{ mV}_{PP}$            | 10   |          |          |          | %          |

| V <sub>FT</sub>                 | V <sub>IN</sub> , V <sub>OUT</sub> Feedthrough<br>in Shutdown | Shutdown Pin = 0V<br>$V_{IN}$ = 4 $V_{PP}$ , 1 MHz<br>$R_L$ = 50 $\Omega$            | -50  |          |          |          | dB         |

| C <sub>OUT</sub>                | Output Capacitance<br>in Shutdown                             | Shutdown Pin = 0V                                                                    | 30   |          |          |          | pF         |

| t <sub>SD</sub>                 | Shutdown<br>Response Time                                     |                                                                                      | 700  |          |          |          | ns         |

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 3: During current limit, thermal limit, or electronic shutdown the input current will increase if the input to output differential voltage exceeds 8V. See Overvoltage Protection in Application Hints.

Note 4: The LM6125 series buffers contain current limit and thermal shutdown to protect against fault conditions.

## AC Electrical Characteristics (Continued)

Note 5: For operation at elevated temperature, these devices must be derated based on a thermal resistance of  $\theta_{JA}$  and  $T_J$  max,  $T_J = T_A + \theta_{JA}$  P<sub>D</sub>.  $\theta_{JC}$  for the LM6125H and LM6225H is 17°C/W. The thermal impedance  $\theta_{IA}$  of the device in the N package is 40°C/W when soldered directly to a printed circuit board, and the heat-sinking pins (pins 3, 4, 5, 10, 11, and 12) are connected to 2 square inches of 2 oz. copper. When installed in a socket, the thermal impedance  $\theta_{JA}$  of the N package is 60°C/W.

Note 6: Limits are guaranteed by testing or correlation.

Note 7: The input is biased to +2.5V, and V<sub>IN</sub> swings V<sub>PP</sub> about this value. The input swing is 2 V<sub>PP</sub> at all temperatures except for the A<sub>V</sub>3 test at -55°C where it is reduced to 1.5 VPP.

Note 8: The Error Flag is set (low) during current limit or thermal fault detection in addition to being set by the Shutdown pin. It is an open-collector output which requires an external pullup resistor.

Note 9: Slew rate is measured with a ±11V input pulse and 50Ω source impedance at 25°C. Since voltage gain is typically 0.9 driving a 50Ω load, the output swing will be approximately ±10V. Slew rate is calculated for transitions between ±5V levels on both rising and falling edges. A high speed measurement is done to minimize device heating. For slew rate versus junction temperature see typical performance curves. The input pulse amplitude should be reduced to ±10V for measurements at temperature extremes. For accurate measurements, the input slew rate should be at least 1700 V/µs.

Note 10: The test circuit consists of the human body model of 120 pF in series with  $1500\Omega$ .

Note 11: A military RETS specification is available on request. At the time of printing, the LM6125H/883 RETS spec complied with the Boldface limits in this column. The LM6125H/883 may also be procured as Standard Military Drawing specification #5962-9081501MXX.

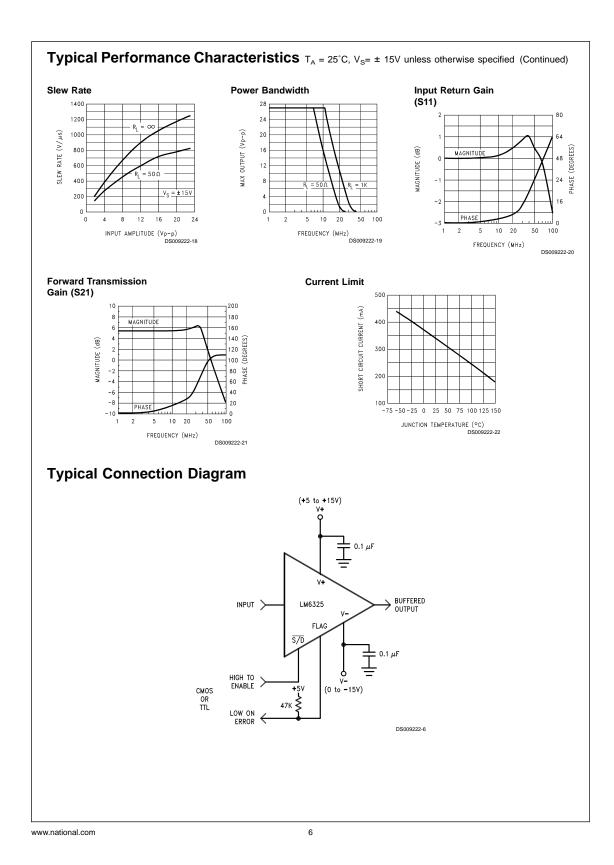

## Typical Performance Characteristics $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ unless otherwise specified

Slew Rate vs Temperature

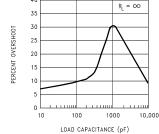

Large Signal Response  $(R_L = 1 k\Omega)$

-3 dB Bandwidth

70

60

50

40

30

20

0 2

-3 dB BANDWIDTH (MHz)

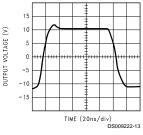

Large Signal Response (R<sub>L</sub> = 50Ω)

www.national.com

4 6 8 10 12 14 16 18 20

SUPPLY VOLTAGE (±V) DS009222-16

## Application Hints

#### POWER SUPPLY DECOUPLING

The method of supply bypassing is not critical for stability of the LM6125 series buffers. However, their high current output combined with high slew rate can result in significant voltage transients on the power supply lines if much inductance is present. For example, a slew rate of 900 V/µs into a 50Ω load produces a di/dt of 18 A/µs. Multiplying this by a wiring inductance of 50 nH results in a 0.9V transient. To minimize this problem use high quality decoupling very close to the device. Suggested values are a 0.1 µF ceramic in parallel with one or two 2.2 µF tantalums. A ground plane is recommended.

#### LOAD IMPEDANCE

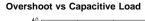

The LM6125 is stable into any load when driven by a  $50\Omega$  source. As shown in the *Overshoot vs Capacitive Load* graph, worst case is a purely capacitive load of about 1000 pF. Shunting the load capacitance with a resistor will reduce overshoot.

#### SOURCE INDUCTANCE

Like any high-frequency buffer, the LM6125 can oscillate at high values of source inductance. The worst case condition occurs at a purely capacitive load of 50 pF where up to 100 nH of source inductance can be tolerated. With a 50 $\Omega$  load, this goes up to 200 nH. This sensitivity may be reduced at the expense of a slight reduction in bandwidth by adding a resistor in series with the buffer input. A 100 $\Omega$  resistor will ensure stability with source inductances up to 400 nH with any load.

#### ERROR FLAG LOGIC

The Error Flag pin is an open-collector output which requires an external pull-up resistor. Flag voltage is HIGH during operation, and is LOW during a fault condition. A fault condition occurs if either the internal current limit or the thermal shutdown is activated, or the shutdown (S/D) pin is driven low by external logic. Flag voltage returns to its HIGH state when normal operation resumes.

If the S/D pin is not to be used, it should be connected to V<sup>+</sup>.

#### **OVERVOLTAGE PROTECTION**

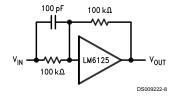

The LM6125 may be severely damaged or destroyed if the Absolute Maximum Rating of 7V between input and output pins is exceeded.

If the buffer's input-to-output differential voltage is allowed to exceed 7V, a base-emitter junction will be in reverse-breakdown, and will be in series with a forward-biased base-emitter junction. Referring to the LM6125 simplified schematic, the transistors involved are Q1 and Q3 for positive inputs, and Q2 and Q4 for negative inputs. If any current is allowed to flow through these junctions, localized heating of the reverse-biased junction will occur, potentially causing damage. The effect of the damage is typically increased offset voltage, increased bias current, and/or degraded AC performance. The damage is cumulative, and may eventually result in complete device failure.

The device is best protected by the insertion of the parallel combination of a 100 k $\Omega$  resistor (R1) and a small capacitor (C1) in series with the buffer input, and a 100 k $\Omega$  resistor (R2) from input to output of the buffer (see *Figure 1*). This network normally has no effect on the buffer output. However, if the buffer's current limit or shutdown is activated, and the output has a ground-referred load of significantly less than 100 k $\Omega$ , a large input-to-output voltage may be present. R1 and R2 then form a voltage divider, keeping the input-output differential below the 7V Maximum Rating for input voltages up to 14V. This protection network should be sufficient to protect the LM6125 from the output of nearly any op amp which is operated on supply voltages of ±15V or lower.

FIGURE 1. LM6125 with Overvoltage Protection

www.national.com

www.national.com

8

Notes

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| National Semiconductor<br>Corporation | National Semiconductor<br>Europe     | National Semiconductor<br>Asia Pacific Customer | National Semiconductor<br>Japan Ltd. |

|---------------------------------------|--------------------------------------|-------------------------------------------------|--------------------------------------|

| Americas                              | Fax: +49 (0) 1 80-530 85 86          | Response Group                                  | Tel: 81-3-5639-7560                  |

| Tel: 1-800-272-9959                   | Email: europe.support@nsc.com        | Tel: 65-2544466                                 | Fax: 81-3-5639-7507                  |

| Fax: 1-800-737-7018                   | Deutsch Tel: +49 (0) 1 80-530 85 85  | Fax: 65-2504466                                 |                                      |

| Email: support@nsc.com                | English Tel: +49 (0) 1 80-532 78 32  | Email: sea.support@nsc.com                      |                                      |

|                                       | Français Tel: +49 (0) 1 80-532 93 58 |                                                 |                                      |

| vww.national.com                      | Italiano Tel: +49 (0) 1 80-534 16 80 |                                                 |                                      |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.