# 14-Bit, 2500 MSPS, RF Digital-to-Analog Converter

AD9739

#### **FEATURES**

#### **Dynamic performance**

#### **DOCSIS 3.0 performance**

8 QAM carriers @ 400 MHz IF: -71 dBc 16 QAM carriers @ 400 MHz IF: -68 dBc 32 QAM carriers @ 400 MHz IF: -65 dBc 72 QAM carriers @ 600 MHz IF: -61 dBc

Single-carrier WCDMA ACLR performance @ 2457.6 MSPS

f<sub>OUT</sub> = 350 MHz (normal mode) 1<sup>st</sup> adjacent channel: -80 dBc 5<sup>th</sup> adjacent channel: -80.5 dBc f<sub>OUT</sub> = 2100 MHz (mix mode)

1st adjacent channel: -69 dBc

5<sup>th</sup> adjacent channel: -75 dBc

Single-tone NSD performance @ 2.4 GSPS

-166 dBm/Hz @ 100 MHz IF -162 dBm/Hz @ 1 GHz IF

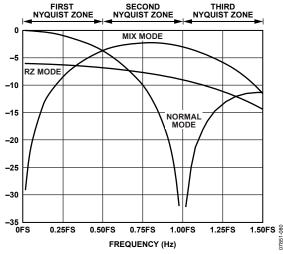

RF synthesis support FS mix, RZ modes

Dual-port LVDS data interface with on-chip 100  $\Omega$  terminations

Low power: 1.1 W @ 2.5 GSPS

#### **APPLICATIONS**

Broadband communications systems

CMTS/VOD

Cellular infrastructure

Point-to-point wireless

Instrumentation, automatic test equipment

Radar, avionics

#### **GENERAL DESCRIPTION**

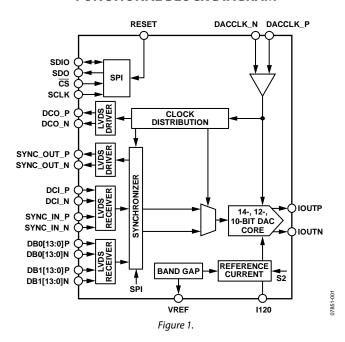

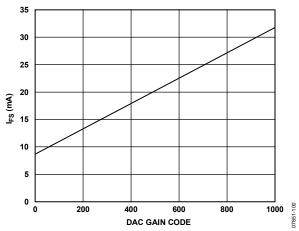

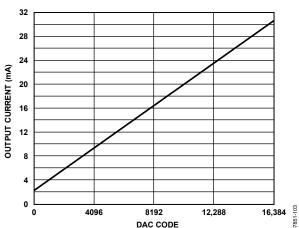

The AD9739 is a high performance, high frequency 14-bit DAC that provides sample rates up to 2500 MSPS, permitting multicarrier generation up to the Nyquist frequency in baseband mode and second and third Nyquist zones in mix mode. It includes a serial peripheral interface (SPI) for configuration and readback of status registers. A dual-port LVDS interface is used to enable the high sample rate with existing FGPA/ASIC technology. The output current can be programmed over a range of 8.66 mA to 31.66 mA. The AD9739 is manufactured on a 0.18  $\mu m$  CMOS process and operates from 1.8 V and 3.3 V supplies. It is supplied in a 160-ball chip scale ball grid array for reduced package parasitics.

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **PRODUCT HIGHLIGHTS**

- 1. Low noise and intermodulation distortion (IMD) performance enable high quality synthesis of wideband signals up to 1 GHz.

- A dual-port interface with double data rate (DDR) LVDS data receivers supports the maximum conversion rate of 2500 MSPS.

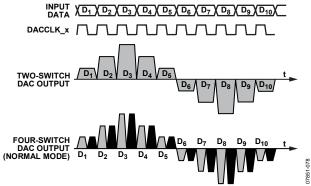

- 3. Manufactured on a CMOS process, the AD9739 uses a proprietary switching technique that enhances dynamic performance.

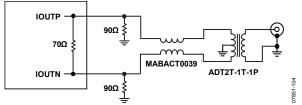

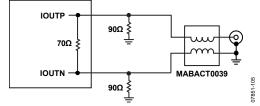

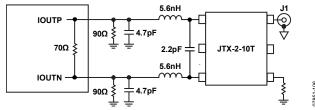

- 4. The current output(s) of the AD9739 are easily configured for single-ended or differential circuit topologies.

## **TABLE OF CONTENTS**

| Features                                                                   | 1  |

|----------------------------------------------------------------------------|----|

| Applications                                                               | 1  |

| General Description                                                        | 1  |

| Functional Block Diagram                                                   | 1  |

| Product Highlights                                                         | 1  |

| Revision History                                                           | 2  |

| Specifications                                                             | 3  |

| DC Specifications                                                          | 3  |

| Digital Specifications                                                     | 4  |

| AC Specifications                                                          | 5  |

| Absolute Maximum Ratings                                                   | 7  |

| Thermal Resistance                                                         | 7  |

| ESD Caution                                                                | 7  |

| Pin Configurations and Function Descriptions                               | 8  |

| Typical Performance Characteristics                                        | 11 |

| Static Linearity                                                           | 11 |

| Dynamic Performance Normal Mode, 20 mA Full Scale (Unless Otherwise Noted) | 13 |

| Dynamic Performance Mix Mode, 20 mA Full Scale                             | 17 |

| DOCSIS Performance                                                         | 19 |

| Terminology                                                                | 24 |

| Theory of Operation                                                        | 25 |

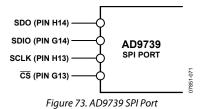

| Serial Peripheral Interface                                                | 25 |

| General Operation of the Serial Interface                                  | 25 |

| Instruction Mode (8-Bit Instruction)                                       | 25 |

| Serial Interface Port Pin Descriptions                                     | 25 |

| SCLK—Serial Clock                                                          | 25 |

| CS—Chip Select                                                             | 25 |

| SDIO—Serial Data I/O                                                       | 25 |

| SDO—Serial Data Out                                                        | 25 |

| MSB/LSB Transfers                                                          | 26 |

| Serial Port Configuration                                                  | 26 |

| SPI Register Map                           |

|--------------------------------------------|

| SPI Registers                              |

| Applications Information                   |

| Analog Modes of Operation                  |

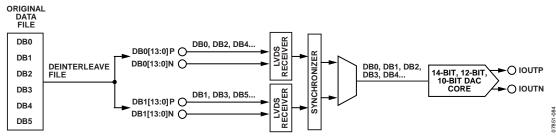

| LVDS Data Port Interface                   |

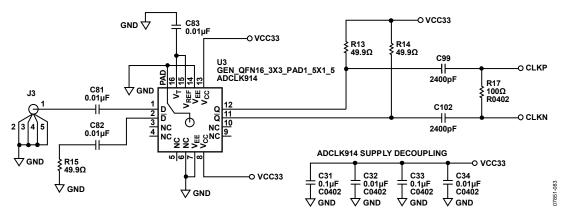

| Clocking the AD973939                      |

| Applying Data to the AD973940              |

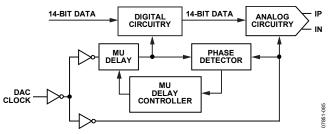

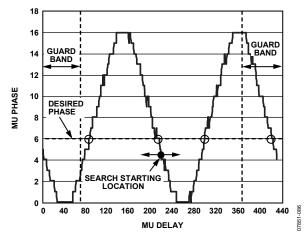

| Mu Delay Controller41                      |

| Mu Control Operation41                     |

| Search Mode                                |

| Track Mode42                               |

| Mu Delay and Phase Readback                |

| Operating the Mu Controller Manually42     |

| Calculating Mu Delay Line Step Size42      |

| Synchronization Controller                 |

| Operation in Master Mode44                 |

| Operation in Slave Mode45                  |

| Data Receiver Operation in Auto Mode45     |

| Data Receiver Operation in Manual Mode46   |

| Data Receiver Operation in Manual Mode     |

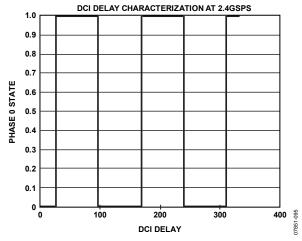

| Calculating the DCI Delay Line Step Size   |

|                                            |

| Calculating the DCI Delay Line Step Size46 |

| Calculating the DCI Delay Line Step Size   |

| Calculating the DCI Delay Line Step Size   |

| Calculating the DCI Delay Line Step Size   |

| Calculating the DCI Delay Line Step Size   |

| Calculating the DCI Delay Line Step Size   |

| Calculating the DCI Delay Line Step Size   |

| Calculating the DCI Delay Line Step Size   |

#### **REVISION HISTORY**

1/09—Revision 0: Initial Version

# **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

VDDA = VDD33 = 3.3 V, VDDC = VDD = 1.8 V,  $I_{FS}$  = 20 mA.

Table 1.

| Parameter                                      | Min  | Тур   | Max   | Unit   |

|------------------------------------------------|------|-------|-------|--------|

| RESOLUTION                                     |      | 14    |       | Bits   |

| ACCURACY                                       |      |       |       |        |

| Integral Nonlinearity (INL)                    |      | ±1.3  |       | LSB    |

| Differential Nonlinearity (DNL)                |      | ±0.8  |       | LSB    |

| ANALOG OUTPUTS                                 |      |       |       |        |

| Gain Error (with Internal Reference)           |      | 5.5   |       | %      |

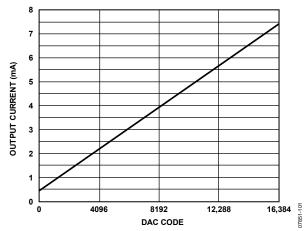

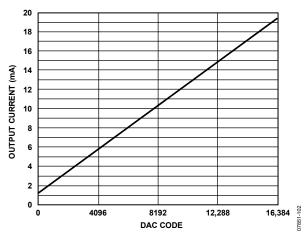

| Full-Scale Output Current                      | 8.66 | 20.2  | 31.66 | mA     |

| Output Compliance Range                        | -1.0 |       | +1.0  | V      |

| Output Resistance                              |      | 10    |       | ΜΩ     |

| Output Capacitance                             |      | 1     |       | pF     |

| TEMPERATURE DRIFT                              |      |       |       |        |

| Gain                                           |      | 60    |       | ppm/°C |

| Reference Voltage                              |      | 20    |       | ppm/°C |

| REFERENCE                                      |      |       |       |        |

| Internal Reference Voltage                     |      | 1.2   |       | V      |

| Output Resistance <sup>1</sup>                 |      | 5     |       | kΩ     |

| ANALOG SUPPLY VOLTAGES                         |      |       |       |        |

| VDDA                                           | 3.1  | 3.3   | 3.5   | V      |

| VDDC                                           | 1.70 | 1.8   | 1.90  | V      |

| DIGITAL SUPPLY VOLTAGES                        |      |       |       |        |

| VDD33                                          | 3.10 | 3.3   | 3.5   | V      |

| VDD                                            | 1.70 | 1.8   | 1.90  | V      |

| SUPPLY CURRENTS AND POWER DISSIPATION 2.0 GSPS |      |       |       |        |

| lvdda                                          |      | 37    | 38    | mA     |

| lvddc                                          |      | 159   | 166   | mA     |

| l <sub>VDD33</sub>                             |      | 34    | 37    | mA     |

| lvdd                                           |      | 233   | 238   | mA     |

| Power Dissipation                              |      | 0.940 | 0.975 | W      |

| Sleep Mode                                     |      |       |       |        |

| I <sub>VDDA</sub>                              |      | 2.5   | 2.75  | mA     |

| Power-Down Mode <sup>2</sup>                   |      |       |       |        |

| I <sub>VDDA</sub>                              |      | 0.02  | 0.135 | mA     |

| lvddc                                          |      | 3.8   |       | mA     |

| I <sub>VDD33</sub>                             |      | 0.5   | 1.3   | mA     |

| lvdd                                           |      | 0.1   | 2.75  | mA     |

| SUPPLY CURRENTS AND POWER DISSIPATION 2.5 GSPS |      |       |       |        |

| $I_{VDDA}$                                     |      | 37    |       | mA     |

| lvddc                                          |      | 223   |       | mA     |

| I <sub>VDD33</sub>                             |      | 34    |       | mA     |

| lvdd                                           |      | 290   |       | mA     |

| Power Dissipation                              |      | 1.16  |       | W      |

$<sup>^1</sup>$  Use an external amplifier to drive any external load.  $^2$  All power-down bits set (Register 0x01, Bit 0, Bit 1, Bit 4, Bit 5; Register 0x02, Bit 3).

#### **DIGITAL SPECIFICATIONS**

$VDDA = VDD33 = 3.3 \text{ V}, VDDC = VDD = 1.8 \text{ V}, I_{FS} = 20 \text{ mA}.$  LVDS drivers and receivers are compliant to the IEEE-1596 reduced range link, unless otherwise noted.

Table 2.

| Parameter                                                                       | Min  | Тур | Max  | Unit     |

|---------------------------------------------------------------------------------|------|-----|------|----------|

| LVDS DATA INPUTS                                                                |      |     |      |          |

| (DB0[13:0]P, DB0[13:0]N, DB1[13:0]P, DB1[13:0]N) DB+ = $V_{IA}$ , DB-= $V_{IB}$ |      |     |      |          |

| Input Voltage Range, $V_{IA}$ or $V_{IB}$                                       | 825  |     | 1575 | mV       |

| Input Differential Threshold, V <sub>IDTH</sub>                                 | -100 |     | +100 | mV       |

| Input Differential Hysteresis, VIDTHH – VIDTHL                                  |      | 20  |      | mV       |

| Receiver Differential Input Impedance, R <sub>IN</sub>                          | 80   |     | 120  | Ω        |

| LVDS Input Rate                                                                 | 1250 |     |      | MSPS     |

| LVDS Minimum Data Valid Period (t <sub>MDE</sub> )                              |      |     | 344  | ps       |

| Input Capacitance                                                               |      | 1.2 |      | pF       |

| LVDS CLOCK INPUT                                                                |      |     |      |          |

| $(DCI_P, DCI_N) DCI_P = V_{IA}, DCI_N = V_{IB}$                                 |      |     |      |          |

| Input Voltage Range, V <sub>IA</sub> or V <sub>IB</sub>                         | 825  |     | 1575 | mV       |

| Input Differential Threshold, VIDTH                                             | -100 |     | +100 | mV       |

| Input Differential Hysteresis, VIDTHH — VIDTHL                                  |      | 20  |      | mV       |

| Receiver Differential Input Impedance, R <sub>IN</sub>                          | 80   |     | 120  | Ω        |

| Maximum Clock Rate                                                              | 625  |     |      | MHz      |

| LVDS CLOCK OUTPUT                                                               |      |     |      |          |

| (DCO_P, DCO_N) DCO_P = $V_{OA}$ , DCO_N = $V_{OB}$ 100 $\Omega$ Termination     |      |     |      |          |

| Output Voltage High, V <sub>OA</sub> or V <sub>OB</sub>                         |      |     | 1375 | mV       |

| Output Voltage Low, V <sub>OA</sub> or V <sub>OB</sub>                          | 1025 |     |      | mV       |

| Output Differential Voltage, $ V_{OD} $                                         | 150  | 200 | 250  | mV       |

| Output Offset Voltage, Vos                                                      | 1150 |     | 1250 | mV       |

| Output Impedance, Single-Ended, R <sub>O</sub>                                  | 40   | 100 | 140  | Ω        |

| $R_{0}$ Mismatch Between A and B, $\Delta RO$                                   |      |     | 10   | %        |

| Change in $ V_{OD} $ Between 0 and 1, $ \Delta V_{OD} $                         |      |     | 25   | mV       |

| Change in $V_{OS}$ Between 0 and 1, $\Delta V_{OS}$                             |      |     | 25   | mV       |

| Output Current, Driver Shorted to Ground, IsA, IsB                              |      |     | 20   | mA       |

| Output Current, Drivers Shorted Together, I <sub>SAB</sub>                      |      |     | 4    | mA       |

| Power-Off Output Leakage,  IXA ,  IXB                                           |      |     | 10   | mA       |

| Maximum Clock Rate                                                              | 625  |     |      | MHz      |

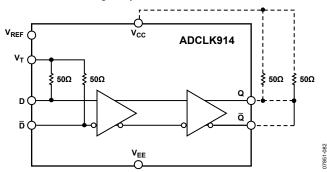

| DAC CLOCK INPUT (DACCLK_P, DACCLK_N)                                            |      |     |      |          |

| Differential Peak-to-Peak Voltage                                               |      | 1.8 |      | V        |

| Common-Mode Voltage                                                             |      | 900 |      | mV       |

| Maximum Clock Rate                                                              |      | 700 |      | 1        |

| VDD = 1.8 V ± 5%                                                                | 800  |     | 2400 | MSPS     |

| $VDD = 1.89 V \pm 5\%$                                                          | 800  |     | 2500 | MSPS     |

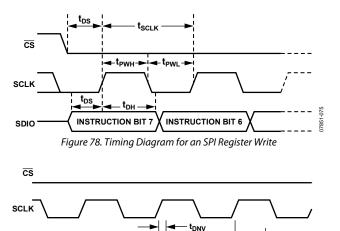

| SERIAL PERIPHERAL INTERFACE                                                     | 000  |     | 2300 | 14151 5  |

| Maximum Clock Rate (f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> )                   |      |     | 20   | MHz      |

| Minimum Pulse Width High, t <sub>PWH</sub>                                      | 20   |     | 20   |          |

| Minimum Pulse Width Low, t <sub>PWL</sub>                                       | 20   |     |      | ns<br>ns |

| Minimum SDIO and CS to SCLK Setup, t <sub>DS</sub>                              | 20   | 10  |      |          |

|                                                                                 |      | 10  |      | ns       |

| Minimum SCLK to SDIO Hold, t <sub>DH</sub>                                      |      | 5   |      | ns       |

| Maximum SCLK to Valid SDIO and SDO, t <sub>DV</sub>                             |      | 20  |      | ns       |

| Minimum SCLK to Invalid SDIO and SDO, t <sub>DNV</sub>                          |      | 5   |      | ns       |

| Parameter                         | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| INPUTS (SDI, SDIO, SCLK, CS)      |     |     |     |      |

| Voltage in High, V <sub>IH</sub>  | 2.0 | 3.3 |     | V    |

| Voltage in Low, V <sub>IL</sub>   |     | 0   | 0.8 | V    |

| Current in High, I <sub>IH</sub>  | -10 |     | +10 | μΑ   |

| Current in Low, I <sub>I</sub> ∟  | -10 |     | +10 | μΑ   |

| SDIO Output                       |     |     |     |      |

| Voltage Out High, V <sub>OH</sub> | 2.4 |     | 3.6 | V    |

| Voltage Out Low, Vol              | 0   |     | 0.4 | V    |

| Current Out High, I <sub>OH</sub> |     | 4   |     | mA   |

| Current Out Low, IoL              |     | 4   |     | mA   |

#### **AC SPECIFICATIONS**

$\label{eq:VDDA} VDDA = VDD33 = 3.3 \text{ V}, VDDC = VDD = 1.8 \text{ V}, I_{FS} = 20 \text{ mA}.$

Table 3.

| Parameter                                                             | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------|-----|------|------|------|

| DYNAMIC PERFORMANCE                                                   |     |      |      |      |

| Maximum Update Rate                                                   | 800 |      | 2500 | MSPS |

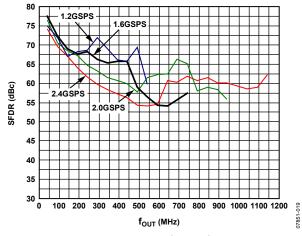

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                    |     |      |      |      |

| $f_{DAC} = 1200 \text{ MSPS}$                                         |     |      |      |      |

| $f_{OUT} = 100 \text{ MHz}$                                           |     | 72   |      | dBc  |

| $f_{OUT} = 350 \text{ MHz}$                                           |     | 69   |      | dBc  |

| $f_{OUT} = 550 \text{ MHz}$                                           |     | 60   |      | dBc  |

| $f_{DAC} = 2000 \text{ MSPS}$                                         |     |      |      |      |

| $f_{OUT} = 70 \text{ MHz}$                                            |     | 76   |      | dBc  |

| $f_{OUT} = 100 \text{ MHz}$                                           |     | 70.5 |      | dBc  |

| $f_{OUT} = 350 \text{ MHz}$                                           |     | 61.5 |      | dBc  |

| $f_{OUT} = 550 \text{ MHz}$                                           |     | 61.5 |      | dBc  |

| $f_{OUT} = 850 \text{ MHz}$                                           |     | 59   |      | dBc  |

| $f_{DAC} = 2400 \text{ MSPS}$                                         |     |      |      |      |

| $f_{OUT} = 100 \text{ MHz}$                                           |     | 69.5 |      | dBc  |

| $f_{OUT} = 350 \text{ MHz}$                                           |     | 58.5 |      | dBc  |

| $f_{OUT} = 550 \text{ MHz}$                                           |     | 54   |      | dBc  |

| $f_{OUT} = 950 \text{ MHz}$                                           |     | 60   |      | dBc  |

| TWO-TONE INTERMODULATION DISTORTION (IMD)                             |     |      |      |      |

| $f_{DAC} = 1200 \text{ MSPS}, f_{OUT2} = f_{OUT1} + 1.25 \text{ MHz}$ |     |      |      |      |

| $f_{OUT} = 100 \text{ MHz}$                                           |     | 92   |      | dBc  |

| $f_{OUT} = 350 \text{ MHz}$                                           |     | 90   |      | dBc  |

| $f_{OUT} = 550 \text{ MHz}$                                           |     | 81   |      | dBc  |

| $f_{DAC} = 2000 \text{ MSPS}, f_{OUT2} = f_{OUT1} + 1.25 \text{ MHz}$ |     |      |      |      |

| $f_{OUT} = 100 \text{ MHz}$                                           |     | 93   |      | dBc  |

| $f_{OUT} = 350 \text{ MHz}$                                           |     | 74   |      | dBc  |

| $f_{OUT} = 550 \text{ MHz}$                                           |     | 71   |      | dBc  |

| $f_{OUT} = 850 \text{ MHz}$                                           |     | 67.5 |      | dBc  |

| $f_{DAC} = 2400 \text{ MSPS}$                                         |     |      |      |      |

| $f_{OUT} = 100 \text{ MHz}$                                           |     | 94   |      | dBc  |

| $f_{OUT} = 350 \text{ MHz}$                                           |     | 78   |      | dBc  |

| $f_{OUT} = 550 \text{ MHz}$                                           |     | 72   |      | dBc  |

| f <sub>OUT</sub> = 950 MHz                                            |     | 68   |      | dBc  |

| Parameter                                                           | Min Typ | Max Unit |

|---------------------------------------------------------------------|---------|----------|

| NOISE SPECTRAL DENSITY (NSD)                                        |         |          |

| Single Tone, f <sub>DAC</sub> = 2400 MSPS                           |         |          |

| $f_{OUT} = 100 \text{ MHz}$                                         | -166    | dBm/Hz   |

| $f_{OUT} = 350MHz$                                                  | -161    | dBm/Hz   |

| $f_{OUT} = 550 \text{ MHz}$                                         | -160    | dBm/Hz   |

| $f_{OUT} = 850 \text{ MHz}$                                         | -160    | dBm/Hz   |

| Eight-Tone, f <sub>DAC</sub> = 2400 MSPS, 500 kHz Tone Spacing      |         |          |

| $f_{OUT} = 100 \text{ MHz}$                                         | -168    | dBm/Hz   |

| $f_{OUT} = 350 \text{ MHz}$                                         | -166    | dBm/Hz   |

| $f_{OUT} = 550 \text{ MHz}$                                         | -166    | dBm/Hz   |

| $f_{OUT} = 850 \text{ MHz}$                                         | -165    | dBm/Hz   |

| WCDMA Adjacent Channel Leakage Ratio (ACLR), Single Carrier         |         |          |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 150 \text{ MHz}$          | 80.5    | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS } f_{OUT} = 350 \text{ MHz}$          | 80      | dBc      |

| $f_{DAC}$ = 2457.6 MSPS, $f_{OUT}$ = 550 MHz                        | 79      | dBc      |

| $f_{DAC}$ = 2457.6 MSPS, $f_{OUT}$ = 950 MHz                        | 78      | dBc      |

| WCDMA Second ACLR, Single Carrier                                   |         |          |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 150 \text{ MHz}$          | 84      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 350 \text{ MHz}$          | 80      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 550 \text{ MHz}$          | 80      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 950 \text{ MHz}$          | 79      | dBc      |

| WCDMA ACLR, Single Carrier<br>(Mix Mode Second Nyquist Zone)        |         |          |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 1300 \text{ MHz}$         | 73.5    | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 1700 \text{ MHz}$         | 73.5    | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 2100 \text{ MHz}$         | 69      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 2400 \text{ MHz}$         | 68      | dBc      |

| WCDMA Second ACLR, Single Carrier<br>(Mix Mode Second Nyquist Zone) |         |          |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 1300 \text{ MHz}$         | 74.5    | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 1700 \text{ MHz}$         | 74      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 2100 \text{ MHz}$         | 72      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 2400 \text{ MHz}$         | 71      | dBc      |

| WCDMA ACLR, Single Carrier<br>(Mix Mode Third Nyquist Zone)         |         |          |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 2500 \text{ MHz}$         | 68      | dBc      |

| $f_{DAC} = 2457$ . MSPS, $f_{OUT} = 2800$ MHz                       | 66      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 3200 \text{ MHz}$         | 66      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS}, f_{OUT} = 3600 \text{ MHz}$         | 64      | dBc      |

| WCDMA ACLR, Single Carrier<br>(Mix Mode Third Nyquist Zone)         |         |          |

| $f_{DAC} = 2457.6 \text{ MSPS, } f_{OUT} = 2500 \text{ MHz}$        | 70      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS, } f_{OUT} = 2800 \text{ MHz}$        | 67      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS, } f_{OUT} = 3200 \text{ MHz}$        | 67      | dBc      |

| $f_{DAC} = 2457.6 \text{ MSPS, } f_{OUT} = 3600 \text{ MHz}$        | 64.5    | dBc      |

#### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Wath Respect To         Rating           VDDA         VSSA         -0.3 V to +3.6 V           VDD33         VSS         -0.3 V to +3.6 V           VDD         VSS         -0.3 V to +1.98 V           VDDC         VSSC         -0.3 V to +1.98 V |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDA         VSSA         -0.3 V to +3.6 V           VDD33         VSS         -0.3 V to +3.6 V           VDD         VSS         -0.3 V to +1.98 V                                                                                                |

| VDD33 VSS -0.3 V to +3.6 V<br>VDD VSS -0.3 V to +1.98 V                                                                                                                                                                                            |

| VDD VSS -0.3 V to +1.98 V                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                    |

| VDDC VSSC 0.3 V to +1.09 V                                                                                                                                                                                                                         |

| VDDC V33C -0.3 V t0 +1.98 V                                                                                                                                                                                                                        |

| VSSA                                                                                                                                                                                                                                               |

| VSSA                                                                                                                                                                                                                                               |

| VSS                                                                                                                                                                                                                                                |

| DACCLK_P, VSSC -0.3 V to CVDD18 + 0.18 V                                                                                                                                                                                                           |

| DACCLK_N                                                                                                                                                                                                                                           |

| DCI, DCO VSS -0.3 V to DVDD33 + 0.3 V                                                                                                                                                                                                              |

| LVDS Data Inputs VSS -0.3 V to DVDD33 + 0.3 V                                                                                                                                                                                                      |

| IOUTP, IOUTN VSSA -1.0 V to AVDD33 + 0.3 V                                                                                                                                                                                                         |

| I120, VREF, IPTAT                                                                                                                                                                                                                                  |

| IRQ, $\overline{CS}$ , SCLK, SDO, VSS $-0.3 \text{ V to DVDD33} + 0.3 \text{ V}$                                                                                                                                                                   |

| SDIO, RESET                                                                                                                                                                                                                                        |

| Junction Temperature 150°C                                                                                                                                                                                                                         |

| Storage Temperature -65°C to +150°C                                                                                                                                                                                                                |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

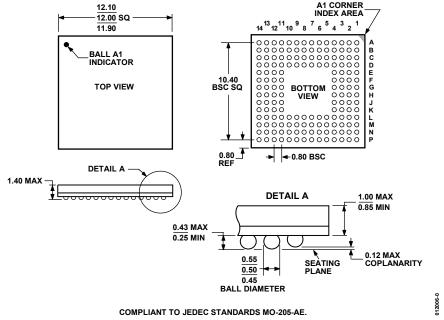

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 5. Thermal Resistance**

| Package Type     | θја  | θις | Unit  |

|------------------|------|-----|-------|

| 160-Ball CSP_BGA | 31.2 | 7.0 | °C/W¹ |

<sup>&</sup>lt;sup>1</sup> With no airflow movement.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

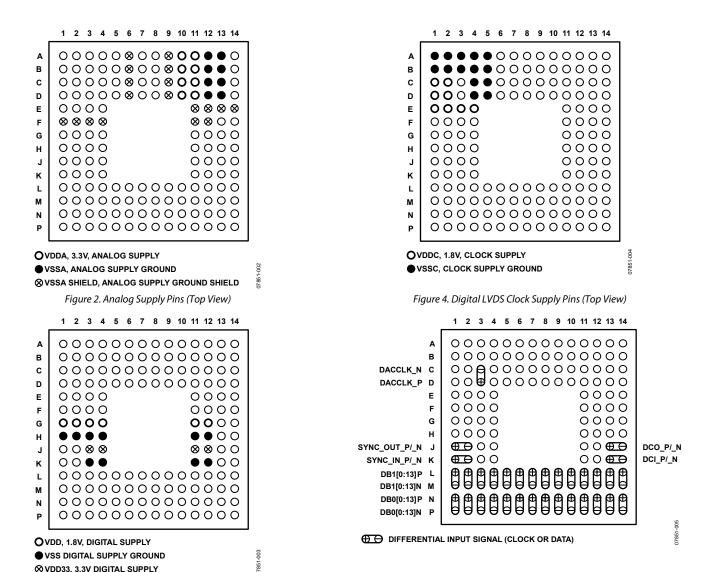

#### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. Digital Supply Pins (Top View)

Figure 5. Digital LVDS Input, Clock I/O (Top View)

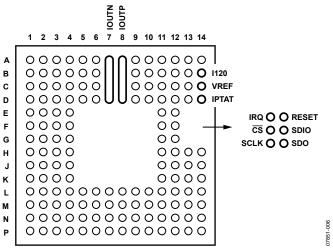

Figure 6. Analog I/O and SPI Control Pins (Top View)

Table 6. AD9739 Pin Function Descriptions

| Table 6. AD9739 Pin Function Descriptions                                    |                       |                                                                                                                                                |  |  |  |  |

|------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No.                                                                      | Mnemonic              | Description                                                                                                                                    |  |  |  |  |

| C1, C2, D1, D2, E1, E2, E3, E4                                               | VDDC                  | 1.8 V Clock Supply.                                                                                                                            |  |  |  |  |

| A1, A2, A3, A4, A5, B1, B2, B3, B4, B5, C4, C5, D4, D5                       | VSSC                  | Clock Supply Ground.                                                                                                                           |  |  |  |  |

| A10, A11, B10, B11, C10, C11, D10, D11                                       | VDDA                  | 3.3 V Analog Supply.                                                                                                                           |  |  |  |  |

| A12, A13, B12, B13, C12, C13, D12, D13,                                      | VSSA                  | Analog Supply Ground.                                                                                                                          |  |  |  |  |

| A6, A9, B6, B9, C6, C9, D6, D9, F1, F2, F3, F4, E11, E12, E13, E14, F11, F12 | VSSA Shield           | Analog Supply Ground Shield. Tie to VSSA at the DAC.                                                                                           |  |  |  |  |

| A14                                                                          | NC                    | No Connect                                                                                                                                     |  |  |  |  |

| A7, B7, C7, D7                                                               | IOUTN                 | DAC Negative Output. 10 mA to 30 mA full-scale output current.                                                                                 |  |  |  |  |

| A8, B8, C8, D8                                                               | IOUTP                 | DAC Positive Output. 10 mA to 30 mA full-scale output current.                                                                                 |  |  |  |  |

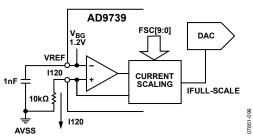

| B14                                                                          | l120                  | Nominal 1.2 V Reference. Tie to analog ground via a 10 k $\Omega$ resistor to generate a 120 $\mu$ A reference current.                        |  |  |  |  |

| C14                                                                          | VREF                  | Band Gap Voltage Reference I/O. Tie to analog ground via a 1 nF capacitor; output impedance is approximately 5 k $\Omega$ .                    |  |  |  |  |

| D14                                                                          | IPTAT                 | Factory Test Pin. Output current, proportional to absolute temperature, is approximately 10 µA at 25°C with a slope of approximately 20 nA/°C. |  |  |  |  |

| C3, D3                                                                       | DACCLK_N/DACCLK_P     | Negative/Positive DAC Clock Input (DACCLK).                                                                                                    |  |  |  |  |

| F13                                                                          | IRQ                   | IRQ. Active low open-drain interrupt request output; pull up to DVDD33 with a 10 k $\Omega$ resistor.                                          |  |  |  |  |

| F14                                                                          | RESET                 | RESET. 1 resets the AD9739.                                                                                                                    |  |  |  |  |

| G13                                                                          | CS                    | See the Serial Peripheral Interface section for the pin description.                                                                           |  |  |  |  |

| G14                                                                          | SDIO                  | See the Serial Peripheral Interface section for the pin description.                                                                           |  |  |  |  |

| H13                                                                          | SCLK                  | See the Serial Peripheral Interface section for the pin description.                                                                           |  |  |  |  |

| H14                                                                          | SDO                   | See the Serial Peripheral Interface section for the pin description.                                                                           |  |  |  |  |

| J3, J4, J11, J12                                                             | VDD33                 | 3.3 V Digital Supply.                                                                                                                          |  |  |  |  |

| G1, G2, G3, G4, G11, G12                                                     | VDD                   | 1.8 V Digital Supply.                                                                                                                          |  |  |  |  |

| H1, H2, H3, H4, H11, H12, K3, K4, K11, K12                                   | VSS                   | Digital Supply Ground.                                                                                                                         |  |  |  |  |

| J1, J2                                                                       | SYNC_OUT_P/SYNC_OUT_N | Positive/Negative SYNC Output (SYNC_OUT). <sup>1</sup>                                                                                         |  |  |  |  |

| K1, K2                                                                       | SYNC_IN_P/SYNC_IN_N   | Positive/Negative SYNC Input (SYNC_IN). <sup>1</sup>                                                                                           |  |  |  |  |

| J13, J14                                                                     | DCO_P/DCO_N           | Positive/Negative Data Output Clock (DCO). <sup>1</sup>                                                                                        |  |  |  |  |

| K13, K14                                                                     | DCI_P/DCI_N           | Positive/Negative Data Input Clock (DCI). <sup>1</sup>                                                                                         |  |  |  |  |

| Pin No.  | Mnemonic          | Description                                  |

|----------|-------------------|----------------------------------------------|

| L1, M1   | DB1[0]P/DB1[0]N   | Port 1 Positive/Negative Data Input Bit 0.1  |

| L2, M2   | DB1[1]P/DB1[1]N   | Port 1 Positive/Negative Data Input Bit 1.1  |

| L3, M3   | DB1[2]P/DB1[2]N   | Port 1 Positive/Negative Data Input Bit 2.1  |

| L4, M4   | DB1[3]P/DB1[3]N   | Port 1 Positive/Negative Data Input Bit 3.1  |

| L5, M5   | DB1[4]P/DB1[4]N   | Port 1 Positive/Negative Data Input Bit 4.1  |

| L6, M6   | DB1[5]P/DB1[5]N   | Port 1 Positive/Negative Data Input Bit 5.1  |

| L7, M7   | DB1[6]P/DB1[6]N   | Port 1 Positive/Negative Data Input Bit 6.1  |

| L8, M8   | DB1[7]P/DB1[7]N   | Port 1 Positive/Negative Data Input Bit 7.1  |

| L9, M9   | DB1[8]P/DB1[8]N   | Port 1 Positive/Negative Data Input Bit 8.1  |

| L10, M10 | DB1[9]P/DB1[9]N   | Port 1 Positive/Negative Data Input Bit 9.1  |

| L11, M11 | DB1[10]P/DB1[10]N | Port 1 Positive/Negative Data Input Bit 10.1 |

| L12, M12 | DB1[11]P/DB1[11]N | Port 1 Positive/Negative Data Input Bit 11.1 |

| L13, M13 | DB1[12]P/DB1[12]N | Port 1 Positive/Negative Data Input Bit 12.1 |

| L14, M14 | DB1[13]P/DB1[13]N | Port 1 Positive/Negative Data Input Bit 13.1 |

| N1, P1   | DB0[0]P/DB0[0]N   | Port 0 Positive/Negative Data Input Bit 0.1  |

| N2, P2   | DB0[1]P/DB0[1]N   | Port 0 Positive/Negative Data Input Bit 1.1  |

| N3, P3   | DB0[2]P/DB0[2]N   | Port 0 Positive/Negative Data Input Bit 2.1  |

| N4, P4   | DB0[3]P/DB0[3]N   | Port 0 Positive/Negative Data Input Bit 3.1  |

| N5, P5   | DB0[4]P/DB0[4]N   | Port 0 Positive/Negative Data Input Bit 4.1  |

| N6, P6   | DB0[5]P/DB0[5]N   | Port 0 Positive/Negative Data Input Bit 5.1  |

| N7, P7   | DB0[6]P/DB0[6]N   | Port 0 Positive/Negative Data Input Bit 6.1  |

| N8, P8   | DB0[7]P/DB0[7]N   | Port 0 Positive/Negative Data Input Bit 7.1  |

| N9, P9   | DB0[8]P/DB0[8]N   | Port 0 Positive/Negative Data Input Bit 8.1  |

| N10, P10 | DB0[9]P/DB0[9]N   | Port 0 Positive/Negative Data Input Bit 9.1  |

| N11, P11 | DB0[10]P/DB0[10]N | Port 0 Positive/Negative Data Input Bit 10.1 |

| N12, P12 | DB0[11]P/DB0[11]N | Port 0 Positive/Negative Data Input Bit 11.1 |

| N13, P13 | DB0[12]P/DB0[12]N | Port 0 Positive/Negative Data Input Bit 12.1 |

| N14, P14 | DB0[13]P/DB0[13]N | Port 0 Positive/Negative Data Input Bit 13.1 |

<sup>&</sup>lt;sup>1</sup> Conforms to IEEE-1596 reduced range link.

### TYPICAL PERFORMANCE CHARACTERISTICS

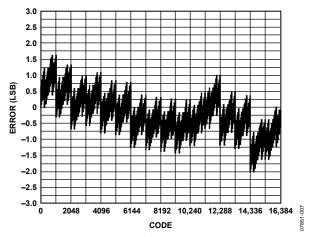

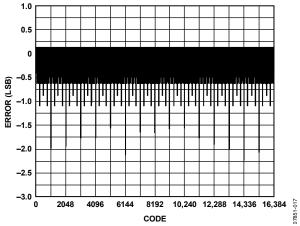

#### **STATIC LINEARITY**

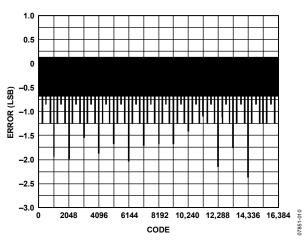

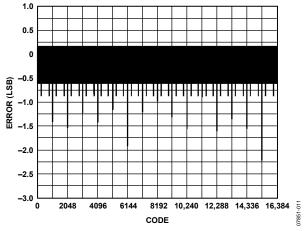

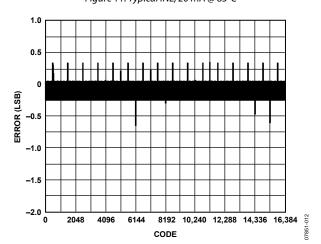

Figure 7. Typical INL, 20 mA @ 25℃

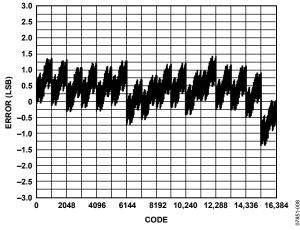

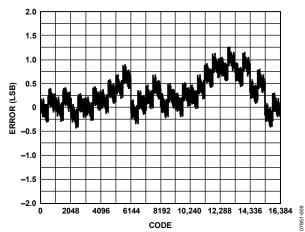

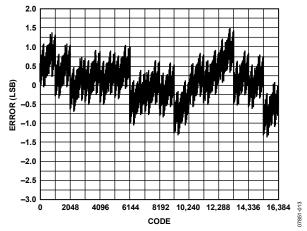

Figure 8. Typical DNL, 20 mA @ 25℃

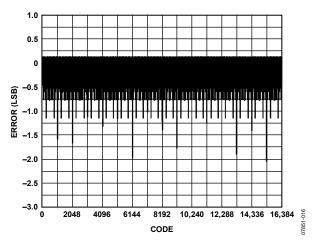

Figure 9. Typical INL, 20 mA @ -40°C

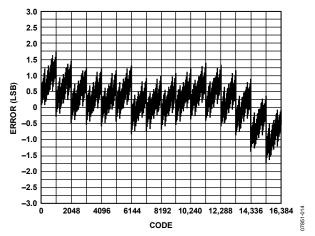

Figure 10. Typical DNL, 20 mA @ −40°C

Figure 11. Typical INL, 20 mA @ 85℃

Figure 12. Typical DNL, 20 mA @ 85°C

Figure 13. Typical INL, 10 mA @ 25℃

Figure 14. Typical DNL, 10 mA @ 25℃

Figure 15. Typical INL, 30 mA @  $25^{\circ}$ C

Figure 16. Typical DNL, 30 mA @ 25°C

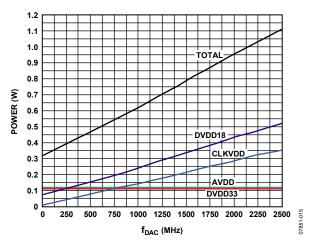

Figure 17. Power Consumption vs.  $f_{DAC} @ 25^{\circ}C$

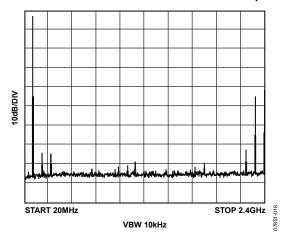

#### DYNAMIC PERFORMANCE NORMAL MODE, 20 MA FULL SCALE (UNLESS OTHERWISE NOTED)

Figure 18. Single Tone Spectrum @  $f_{OUT} = 91$  MHz,  $f_{DAC} = 2.4$  GSPS

Figure 19. Single Tone Spectrum @  $f_{OUT} = 1091$  MHz,  $f_{DAC} = 2.4$  GSPS

Figure 20. SFDR vs.  $f_{OUT}$  over  $f_{DAC}$

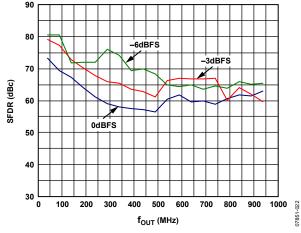

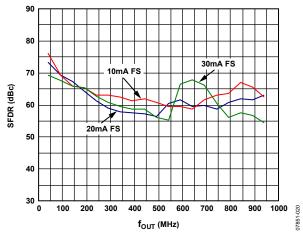

Figure 21. SFDR vs. fout over DIGFS @ 2.0 GSPS

Figure 22. SFDR for Second Harmonic over  $f_{OUT}$  WRT DIGFS @ 2.0 GSPS

Figure 23. SFDR for Third Harmonic over  $f_{OUT}$  WRT DIGFS @ 2.0 GSPS

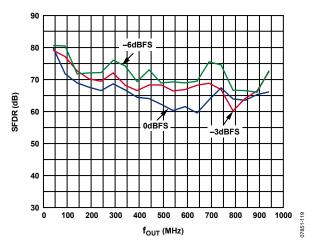

Figure 24. SFDR vs. f<sub>OUT</sub> over ANAFS @ 2.0 GSPS

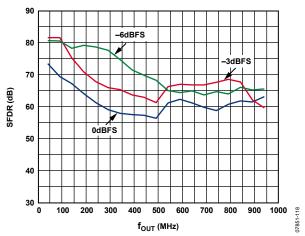

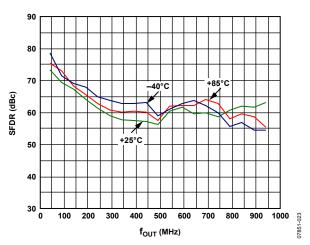

Figure 25. SFDR vs. f<sub>OUT</sub> over Temperature @ 2.0 GSPS

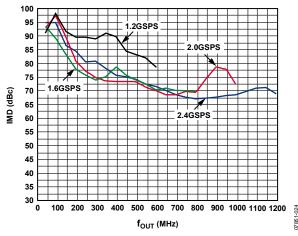

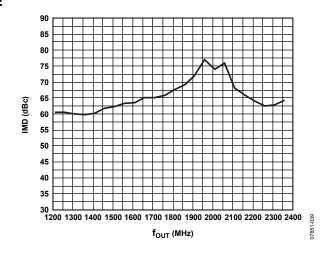

Figure 26. IMD vs. fout over fDAC

Figure 27. IMD vs. fout over DIGFS @ 2.0 GSPS

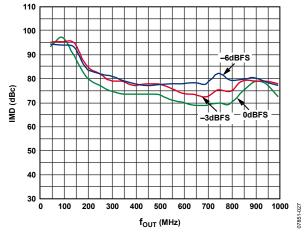

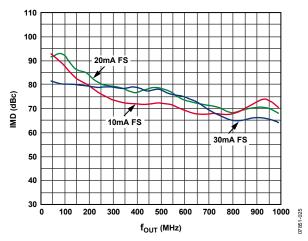

Figure 28. IMD vs. f<sub>OUT</sub> over ANAFS @ 2.0 GSPS

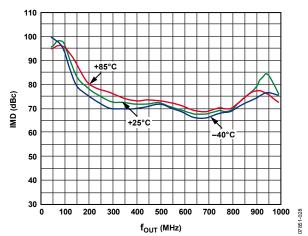

Figure 29. IMD vs. f<sub>OUT</sub> over Temperature @ 2.0 GSPS

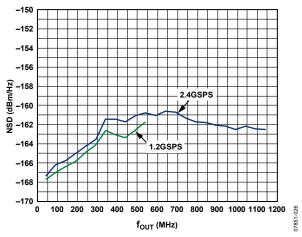

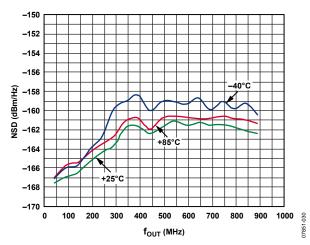

Figure 30. Single-Tone NSD vs. fout over fDAC

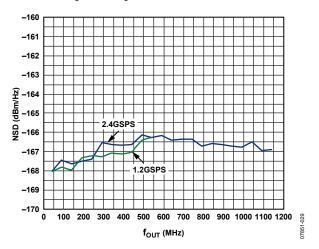

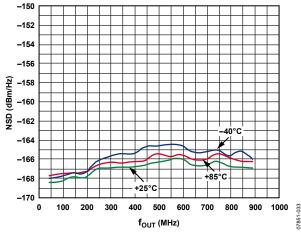

Figure 31. Eight-Tone NSD vs. f<sub>OUT</sub> over f<sub>DAC</sub>

Figure 32. Single-Tone NSD vs.  $f_{OUT}$  over Temperature @ 2.0 GSPS

Figure 33. Eight-Tone NSD vs.  $f_{OUT}$  over Temperature @ 2.0 GSPS

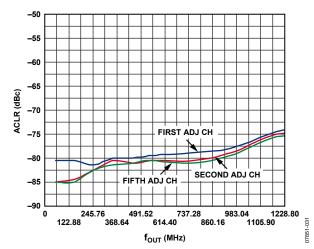

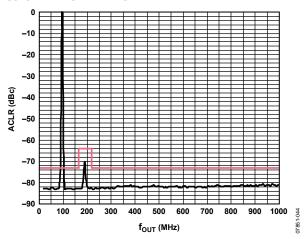

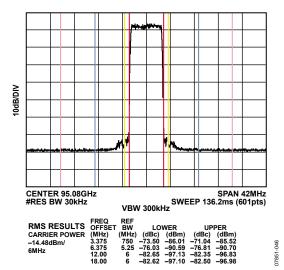

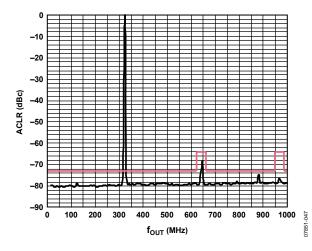

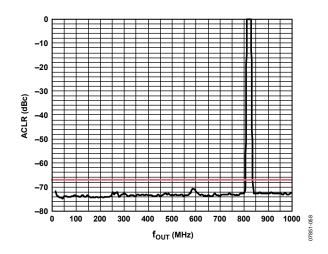

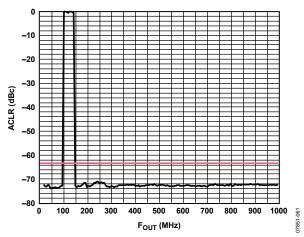

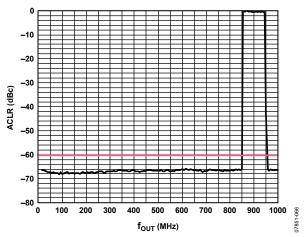

Figure 34. Single-Carrier WCDMA ACLR vs. fout @ 2457.6 MSPS

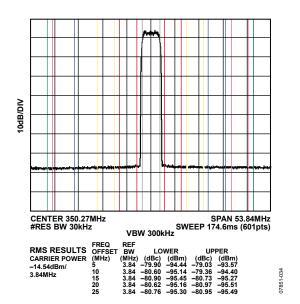

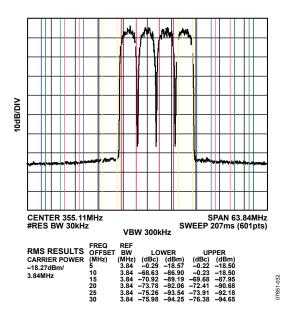

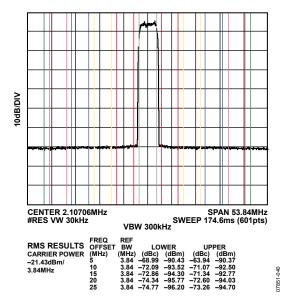

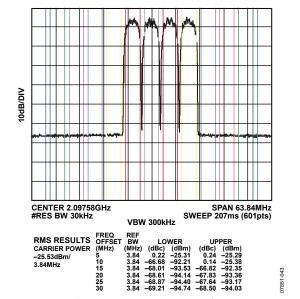

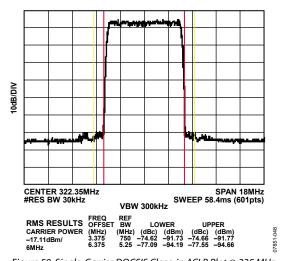

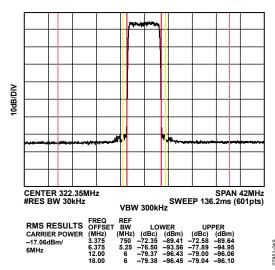

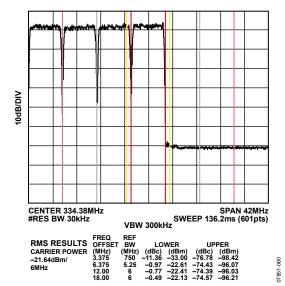

Figure 35. Typical Single-Carrier WCDMA ACLR Performance @ 350 MHz  $f_{\rm DAC}$  = 2457.6 MSPS

Figure 36. Typical Four-Carrier WCDMA ACLR Performance @ 350 MHz,  $f_{\rm DAC}$  = 2457.6 MSPS

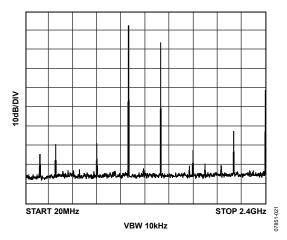

#### **DYNAMIC PERFORMANCE MIX MODE, 20 mA FULL SCALE**

Figure 37. Single-Tone Spectrum in Mix Mode @  $f_{OUT}$  = 2.31 GHz,  $f_{DAC}$  = 2.4 GSPS

Figure 38. Single-Tone Spectrum in Mix Mode @  $f_{OUT}$  = 1.31 GHz,  $f_{DAC}$  = 2.4 GSPS

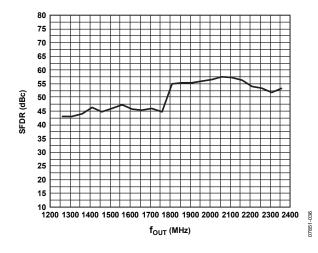

Figure 39. SFDR in Mix Mode vs. fout @ 2.4 GSPS

Figure 40. IMD in Mix Mode vs.  $f_{OUT}$  @ 2.4 GSPS

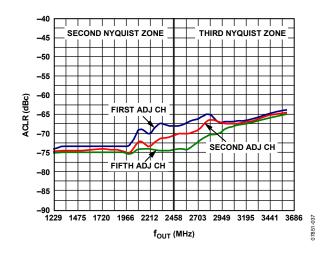

Figure 41. Single-Carrier WCDMA ACLR vs.  $f_{OUT}$  @ 2457.6 MSPS

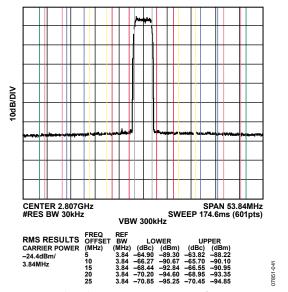

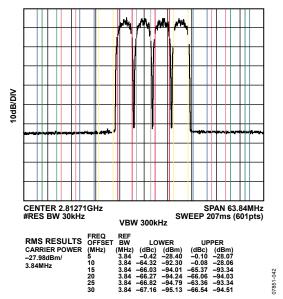

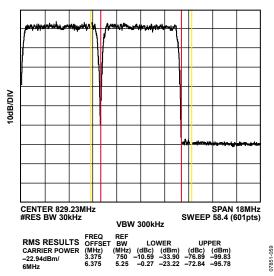

Figure 42. Typical Single-Carrier WCDMA ACLR Performance @ 2.1 GHz,  $f_{DAC}$  = 2457.6 MSPS (Second Nyquist Zone)

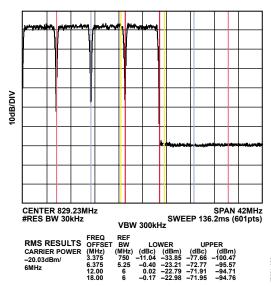

Figure 43. Typical Single-Carrier WCDMA ACLR Performance @ 2.8 GHz,  $f_{DAC}$  = 2457.6 MSPS (Third Nyquist Zone)

Figure 44. Typical Four-Carrier WCDMA ACLR Performance @ 2.1 GHz,  $f_{DAC} = 2457.6$  MSPS (Second Nyquist Zone)

Figure 45. Typical Four-Carrier WCDMA ACLR Performance @ 2.8 GHz  $f_{DAC} = 2457.6$  MSPS (Third Nyquist Zone)

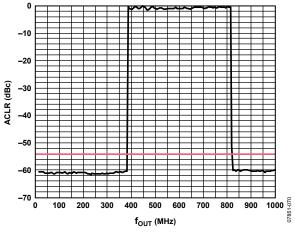

#### **DOCSIS PERFORMANCE**

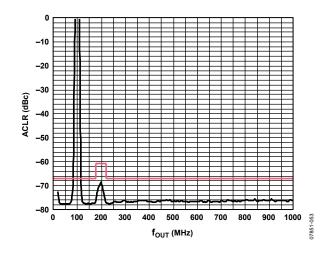

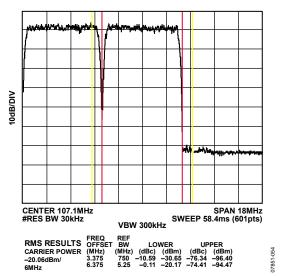

Figure 46. Single-Carrier DOCSIS ACLR Spectral Plot @ 91 MHz (DOCSIS SPEC (Red Line) Is 73 dBc; Harmonic Exception Is 63 dBc)

Figure 47. Single-Carrier DOCSIS Close-in ACLR Plot @ 91 MHz (Two Closest Channels)

Figure 48. Single-Carrier DOCSIS Close-in ACLR Plot @ 91 MHz

Figure 49. Single-Carrier DOCSIS ACLR Spectral Plot @ 325 MHz (DOCSIS SPEC (Red Line) Is 73 dBc; Harmonic Exception Is 63 dBc)

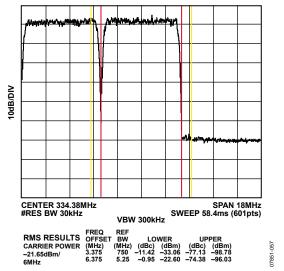

Figure 50. Single-Carrier DOCSIS Close-in ACLR Plot @ 325 MHz (Two Closest Channels)

Figure 51. Single-Carrier DOCSIS Close-in ACLR Plot @ 325 MHz

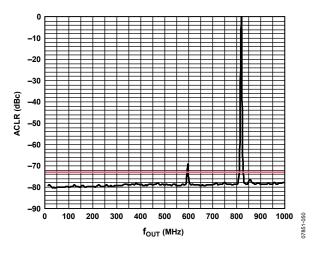

Figure 52. Single-Carrier DOCSIS ACLR Spectral Plot @ 825 MHz (DOCSIS SPEC (Red Line) Is 73 dBc; Harmonic Exception Is 63 dBc)

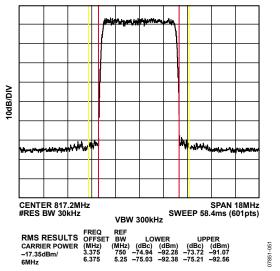

Figure 53. Single-Carrier DOCSIS Close-in ACLR Plot @ 825 MHz (Two Closest Channels)

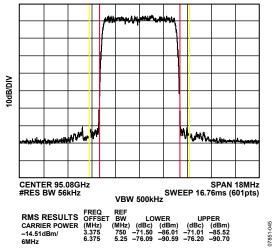

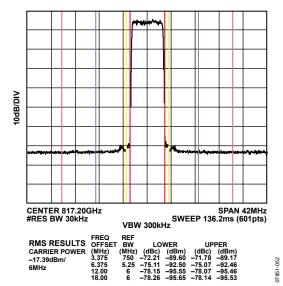

Figure 54. Single-Carrier DOCSIS Close-in ACLR Plot @ 825 MHz

Figure 55. Four-Carrier DOCSIS ACLR Spectral Plot @ 91 MHz (DOCSIS SPEC (Red Line) Is 67 dBc; Harmonic Exception Is 61 dBc)

Figure 56. Four-Carrier DOCSIS Close-in ACLR Plot @ 91 MHz (Two Closest Channels)

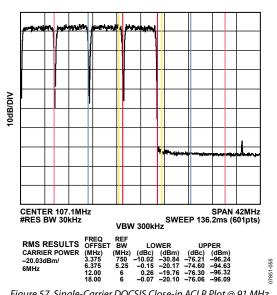

Figure 57. Single-Carrier DOCSIS Close-in ACLR Plot @ 91 MHz

Figure 58. Four-Carrier DOCSIS ACLR Spectral Plot @ 325 MHz (DOCSIS SPEC (Red Line) Is 67 dBc; Harmonic Exception Is 6 1dBc)

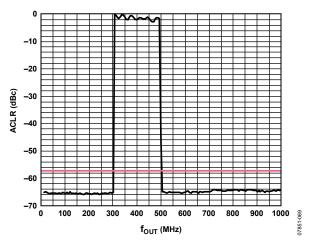

Figure 59. Four-Carrier DOCSIS Close-in ACLR Plot @ 325 MHz (Two Closest Channels)

Figure 60. Single-Carrier DOCSIS Close-in ACLR Plot @ 325 MHz

Figure 61. Four-Carrier DOCSIS ACLR Spectral Plot @ 825 MHz (DOCSIS SPEC (Red Line) Is 67 dBc; Harmonic Exception Is 61 dBc)

Figure 62. Four-Carrier DOCSIS Close-in ACLR Plot @ 825 MHz (Two Closest Channels)

Figure 63. Single-Carrier DOCSIS Close-in ACLR Plot @ 825 MHz

Figure 64. Eight-Carrier DOCSIS ACLR Spectral Plot @ 100 MHz (DOCSIS SPEC (Red Line) Is 63 dBc; Harmonic Exception Is 54 dBc)

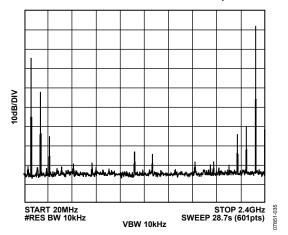

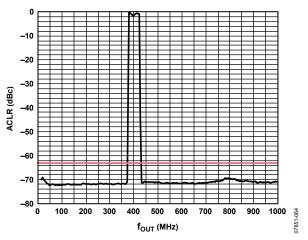

Figure 65. Eight-Carrier DOCSIS ACLR Spectral Plot @ 400 MHz (DOCSIS SPEC (Red Line) Is 63 dBc; Harmonic Exception Is 54 dBc)

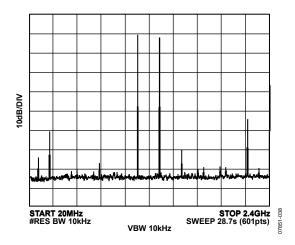

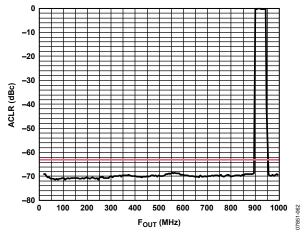

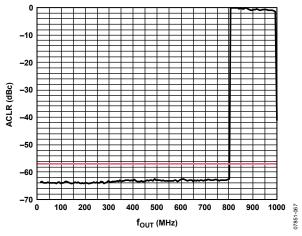

Figure 66. Eight-Carrier DOCSIS ACLR Spectral Plot @ 900 MHz (DOCSIS SPEC (Red Line) Is 63 dBc; Harmonic Exception Is 54 dBc)

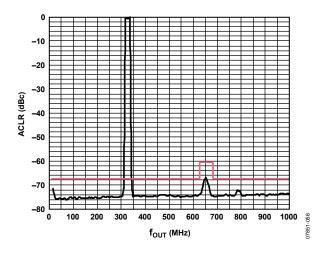

Figure 67. 16-Carrier DOCSIS ACLR Spectral Plot @ 400 MHz (DOCSIS SPEC (Red Line) Is 60 dBc; Harmonic Exception Is 48 dBc)

Figure 68. 16-Carrier DOCSIS ACLR Spectral Plot @ 900 MHz (DOCSIS SPEC (Red Line) Is 60 dBc; Harmonic Exception Is 48 dBc)

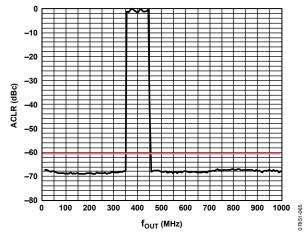

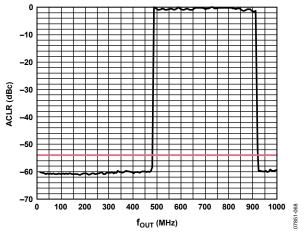

Figure 69. 32-Carrier DOCSIS ACLR Spectral Plot @ 400 MHz (DOCSIS SPEC (Red Line) Is 57 dBc; Harmonic Exception Is 42 dBc)

Figure 70. 32-Carrier DOCSIS ACLR Spectral Plot @ 900 MHz (DOCSIS SPEC (Red Line) Is 57 dBc; Harmonic Exception Is 42 dBc)

Figure 71. 72-Carrier DOCSIS ACLR Spectral Plot @ 600 MHz (DOCSIS SPEC (Red Line) Is 54 dBc; Harmonic Exception Is 35 dBc)

Figure 72. 72-Carrier DOCSIS ACLR Spectral Plot @ 700 MHz (DOCSIS SPEC (Red Line) Is 54 dBc; Harmonic Exception Is 35 dBc)

#### **TERMINOLOGY**

#### Linearity Error (Integral Nonlinearity or INL)

The maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero to full scale.

#### Differential Nonlinearity (DNL)

The measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

#### Monotonicity

A DAC is monotonic if the output either increases or remains constant as the digital input increases.

#### **Offset Error**

The deviation of the output current from the ideal of zero is called the offset error. For IOUTP, 0 mA output is expected when the inputs are all 0s. For IOUTN, 0 mA output is expected when all inputs are set to 1.

#### **Gain Error**

The difference between the actual and ideal output span. The actual span is determined by the output when all inputs are set to 1 minus the output when all inputs are set to 0.

#### **Output Compliance Range**

The range of allowable voltage at the output of a current output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation or breakdown, resulting in nonlinear performance.

#### **Temperature Drift**

Specified as the maximum change from the ambient (25°C) value to the value at either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per °C. For reference drift, the drift is reported in ppm per °C.

#### **Power Supply Rejection**

The maximum change in the full-scale output as the supplies are varied from nominal to minimum and maximum specified voltages.

#### Spurious-Free Dynamic Range

The difference, in decibels (dB), between the rms amplitude of the output signal and the peak spurious signal over the specified bandwidth.

#### **Total Harmonic Distortion (THD)**

The ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal. It is expressed as a percentage or in decibels (dB).

#### Noise Spectral Density (NSD)

NSD is the converter noise power per unit of bandwidth. This is usually specified in dBm/Hz in the presence of a 0 dBm full-scale signal.

#### Adjacent Channel Leakage Ratio (ACLR)

The adjacent channel leakage (power) ratio is a ratio, in dBc, between the measured power within a channel relative to its adjacent channels.

#### **Modulation Error Ratio (MER)**

Modulated signals create a discrete set of output values referred to as a constellation. Each symbol creates an output signal corresponding to one point on the constellation. MER is a measure of the discrepancy between the average output symbol magnitude and the rms error magnitude of the individual symbol.

#### Intermodulation Distortion (IMD)

IMD is the result of two or more signals at different frequencies mixing together. Many products are created according to the formula aF1 $\pm$  bF2, where a and b are integer values.

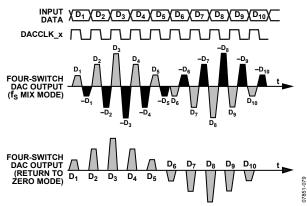

#### THEORY OF OPERATION

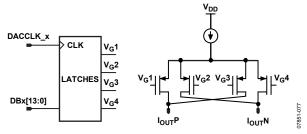

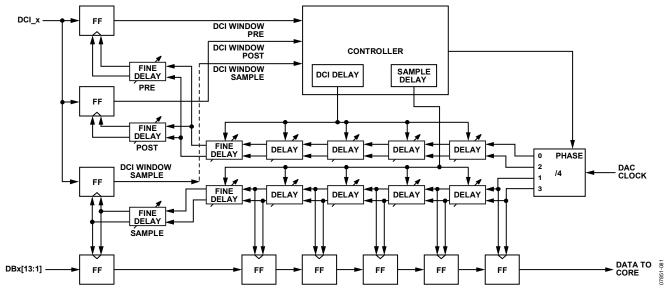

The AD9739 is a 14-bit DAC that operates at an update rate of up to 2.5 GSPS. Due to internal timing requirements, the minimum allowable sample rate is 800 MSPS. Input data is sampled through two 14-bit LVDS ports that are internally multiplexed. Each port has its own data inputs, but both ports share a common DCI input. The LVDS inputs meet the IEEE-1596 reduced swing specification with the exception of input hysteresis, which is not guaranteed over all process corners. Each DCI input runs at one-quarter the input data rate in a double data rate (DDR) format. Each edge of DCI is used to transfer data into the AD9739.

The DACCLK\_N/DACCLK\_P inputs directly drive the DAC core to minimize clock jitter. The DACCLK signal is divided by 4 then output as the DCO for each port. The DCO signal can be used to clock the data source. The DAC expects DDR LVDS data (DB0[13:0], DB1[13:0]), with each channel aligned with the single DDR data input clock (DCI).

Control of the AD9739 functions is via a serial peripheral interface (SPI).

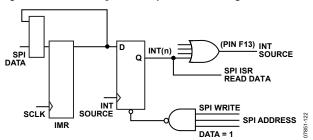

#### SERIAL PERIPHERAL INTERFACE

The AD9739 serial port is a flexible, synchronous serial communications port, allowing easy interface to many industry-standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including the Motorola® SPI and the Intel® SSR protocols. The interface allows read/write access to all registers that configure the AD9739. Most significant bit first (MSB-first) or least significant bit first (LSB-first) transfer formats are supported. The AD9739 serial interface port can be configured as a single pin I/O (SDIO) or two unidirectional pins for input/output (SDIO/SDO).

#### **GENERAL OPERATION OF THE SERIAL INTERFACE**

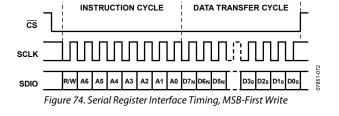

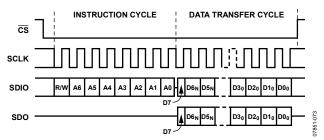

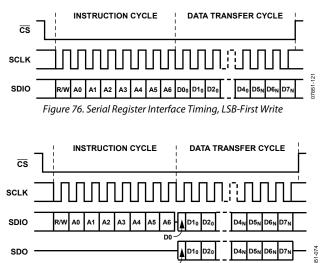

There are two phases to a communication cycle with the AD9739. Phase 1 is the instruction cycle, which is the writing of an instruction byte into the AD9739 coincident with the first eight SCLK rising edges. The instruction byte provides the AD9739 serial port controller with information about the data transfer cycle, which is Phase 2 of the communication cycle. The Phase 1 instruction byte defines whether the upcoming data transfer is read or write and the starting register address for the first byte of the data transfer. The first eight SCLK rising edges of each communication cycle are used to write the instruction byte into the AD9739.

The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the AD9739 and the system controller. Phase 2 of the communication cycle is a transfer of one byte only. Single-byte data transfers are useful to reduce CPU overhead when register access requires one byte only. Registers change immediately upon writing to the last bit of each transfer byte.  $\overline{CS}$  (chip select) can be raised after each sequence of eight bits (except the last byte) to stall the bus. The serial transfer resumes when  $\overline{CS}$  is lowered. Stalling on nonbyte boundaries resets the SPI.

#### **INSTRUCTION MODE (8-BIT INSTRUCTION)**

The instruction byte is shown in the following table.

| M2R |    |    |    |    |    |    | LZR |  |

|-----|----|----|----|----|----|----|-----|--|

| 17  | 16 | 15 | 14 | 13 | 12 | l1 | 10  |  |

| R/W | A6 | A5 | A4 | А3 | A2 | A1 | A0  |  |

R/W, Bit 7 of the instruction byte, determines whether a read or a write data transfer occurs after the instruction byte write. Logic 1 indicates a read operation. Logic 0 indicates a write operation, the data transfer cycle. A6 to A0 (Bit 6 through Bit 0 of the instruction byte) determine which register is accessed during the data transfer portion of the communications cycle.

# SERIAL INTERFACE PORT PIN DESCRIPTIONS SCLK—Serial Clock

The serial clock pin is used to synchronize data to and from the AD9739 and to run the internal state machines. The maximum frequency of SCLK is 20 MHz. All data input to the AD9739 is registered on the rising edge of SCLK. All data is driven out of the AD9739 on the rising edge of SCLK.

#### **CS**—Chip Select

Active low input starts and gates a communication cycle. It allows more than one device to be used on the same serial communications lines. The SDO and SDIO pins go to a high impedance state when this input is high. Chip select should stay low during the entire communication cycle.

#### SDIO—Serial Data I/O

Data is always written into the AD9739 on this pin. However, this pin can be used as a bidirectional data line. The configuration of this pin is controlled by SDIO\_DIR at Register 0x00, Bit 7. The default is Logic 0, which configures the SDIO pin as unidirectional.

#### SDO—Serial Data Out

Data is read from this pin for protocols that use separate lines for transmitting and receiving data. In the case where the AD9739 operates in a single bidirectional I/O mode, this pin does not output data and is set to a high impedance state.

#### MSB/LSB TRANSFERS

The AD9739 serial port can support both MSB-first and LSB-first data formats. This functionality is controlled by LSB/MSB at Register 0x00, Bit 6. The default is MSB first (LSB/MSB = 0). When LSB/MSB = 0 (MSB first), the instruction and data bytes must be written from the most significant bit to the least significant bit.

When LSB/MSB = 1 (LSB first), the instruction and data bytes must be written from the least significant bit to the most significant bit.

#### **SERIAL PORT CONFIGURATION**

The AD9739 serial port configuration is controlled by Register 0x00, Bits[7:5]. Note that the configuration changes immediately upon writing to the last bit of the register. When setting the software reset (Register 0x00, Bit 5), all registers are set to their default values except Register 0x00, which remains unchanged.

In the event of unexpected programming sequences, the AD9739 SPI can become inaccessible. For example, if user code inadvertently changes the LSB/MSB bit, the following bits experience unexpected results. The SPI can be returned to a known state by writing an incomplete byte (1 to 7 bits) of all 0s followed by three bytes of 0x00. This returns to the MSB-first instructions (Register 0 x00 = 0x00) so that the device can be reinitialized.

Figure 75. Serial Register Interface Timing, MSB-First Read

Figure 77. Serial Register Interface Timing, LSB-First Read

Figure 79. Timing Diagram for an SPI Register Read

After the last instruction bit is written to the SDIO pin, the driving signal must be set to a high impedance in time for the bus to turn around. The serial output data from the AD9739 is enabled by the falling edge of SCLK. This causes the first output data bit to be shorter than the remaining data bits, as shown in Figure 79. To assure proper reading of data, read the SDIO or SDO pin prior to changing the SCLK from low to high. Due to the more complex multibyte protocol, multiple AD9739 devices cannot be daisy-chained on the SPI bus. Multiple DACs should be controlled by independent  $\overline{\text{CS}}$  signals.

SDIO I1

# **SPI REGISTER MAP**

Table 7.

| Name               | Address | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1               | Bit 0               | Default |

|--------------------|---------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------|

| Mode               | 0x00    | SDIO_DIR            | LSB/MSB             | Reset               | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | 0x00    |

| Power-<br>Down     | 0x01    | N/A                 | N/A                 | LVDS_DCO<br>_PD     | LVDS_RCVR<br>_PD    | N/A                 | N/A                 | CLK_REC_<br>PD      | DAC_BIAS<br>_PD     | 0x00    |

| CNT_CLK_<br>Dis    | 0x02    | N/A                 | N/A                 | N/A                 | N/A                 | CLKGEN<br>_PD       | N/A                 | REC_CNT_<br>CLK     | MU_CNT_<br>CLK      | 0x03    |

| IRQ_En             | 0x03    | N/A                 | N/A                 | SYNC_LST<br>_EN     | SYNC_LCK<br>_EN     | MULST_EN            | MULCK_EN            | RCV_<br>LST_EN      | RCV_<br>LCK_EN      | 0x00    |

| IRQ_Req            | 0x04    | N/A                 | N/A                 | SYNC_LST<br>_IRQ    | SYNC_LCK<br>_IRQ    | MULST<br>_IRQ       | MULCK<br>_IRQ       | RCVLST<br>_IRQ      | RCVLCK<br>_IRQ      | 0x00    |

| RSVD               | 0x05    | N/A                 | N/A     |

| FSC_1              | 0x06    | FSC[7]              | FSC[6]              | FSC[5]              | FSC[4]              | FSC[3]              | FSC[2]              | FSC[1]              | FSC[0]              | 0x00    |

| FSC_2              | 0x07    | Sleep               | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | FSC[9]              | FSC[8]              | 0x02    |

| Dec_CNT            | 0x08    | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | N/A                 | DAC_DEC<br>[1]      | DAC_DEC<br>[0]      | 0x00    |

| RSVD               | 0x09    | N/A                 | N/A     |

| LVDS_CNT           | 0x0A    | N/A                 | N/A                 | N/A                 | N/A                 | HNDOFF_<br>CHK_RST  | N/A                 | LVDS_<br>Bias[1]    | LVDS_<br>Bias[0]    | 0x00    |

| DIG_STAT           | 0x0B    | HNDOFF_<br>Fall[3]  | HNDOFF_<br>Fall[2]  | HNDOFF_<br>Fall[1]  | HNDOFF_<br>Fall[0]  | HNDOFF_<br>Rise[3]  | HNDOFF_<br>Rise[2]  | HNDOFF_<br>Rise[1]  | HNDOFF_<br>Rise[0]  | RNDM    |

| LVDS_<br>STAT1     | 0x0C    | SUP/HLD_<br>Edge1   | N/A                 | DCI_PHS3            | DCI_PHS1            | DCI_PRE<br>_PH2     | DCI_PRE<br>_PH0     | DCI_PST<br>_PH2     | DCI_PST<br>_PH0     | RNDM    |

| LVDS_<br>STAT2     | 0x0D    | SUP/HLD_<br>SYNC    | SUP/HLD_<br>Edge0   | SYNC_<br>SAMP1      | SYNC_<br>SAMP0      | LVDS1_HI            | LVDS1_LO            | LVDS0_HI            | LVDS0_LO            | RNDM/0  |

| RSVD               | 0x0E    | N/A                 | N/A     |

| RSVD               | 0x0F    | N/A                 | N/A     |

| LVDS_<br>REC_CNT1  | 0x10    | SYNC_<br>FLG_RST    | SYNC_<br>LOOP_ON    | SYNC_<br>MST/SLV    | SYNC_<br>CNT_ENA    | N/A                 | RCVR_FLG<br>_RST    | RCVR_<br>LOOP_ON    | RCVR_<br>CNT_ENA    | 0x42    |

| LVDS_<br>REC_CNT2  | 0x11    | SMP_DEL<br>[1]      | SMP_DEL<br>[0]      | FINE_DEL_<br>MID[3] | FINE_DEL_<br>MID[2] | FINE_DEL_<br>MID[1] | FINE_DEL_<br>MID[0] | RCVR_<br>GAIN[1]    | RCVR_<br>GAIN[0]    | 0xDD    |

| LVDS_<br>REC_CNT3  | 0x12    | SMP_DEL<br>[9]      | SMP_DEL<br>[8]      | SMP_DEL<br>[7]      | SMP_DEL<br>[6]      | SMP_DEL<br>[5]      | SMP_DEL<br>[4]      | SMP_DEL<br>[3]      | SMP_DEL<br>[2]      | 0x29    |

| LVDS_<br>REC_CNT4  | 0x13    | DCI_DEL[3]          | DCI_DEL[2]          | DCI_DEL[1]          | DCI_DEL[0]          | FINE_DEL_<br>SKW[3] | FINE_DEL_<br>SKW[2] | FINE_DEL_<br>SKW[1] | FINE_DEL_<br>SKW[0] | 0x71    |

| LVDS_<br>REC_CNT5  | 0x14    | CLKDIVPH<br>[1]     | CLKDIVPH<br>[0]     | DCI_DEL[9]          | DCI_DEL[8]          | DCI_DEL[7]          | DCI_DEL[6]          | DCI_DEL[5]          | DCI_DEL[4]          | 0x0A    |

| LVDS_<br>REC_CNT6  | 0x15    | SYNC_<br>GAIN[1]    | SYNC_<br>GAIN[0]    | SYNCOUT_<br>PH[1]   | SYNCOUT_<br>PH[0]   | LCKTHR[3]           | LCKTHR[2]           | LCKTHR[1]           | LCKTHR[0]           | 0x42    |

| LVDS_<br>REC_CNT7  | 0x16    | N/A                 | SYNCO_<br>DEL[6]    | SYNCO_<br>DEL[5]    | SYNCO_<br>DEL[4]    | SYNCO_<br>DEL[3]    | SYNCO_<br>DEL[2]    | SYNCO_<br>DEL[1]    | SYNCO_<br>DEL[0]    | 0x00    |

| LVDS_<br>REC_CNT8  | 0x17    | SYNCSH_<br>DEL[0]   | N/A                 | 0x00    |

| LVDS_<br>REC_CNT9  | 0x18    | SYNCSH_<br>DEL[8]   | SYNCSH_<br>DEL[7]   | SYNCSH_<br>DEL[6]   | SYNCSH_<br>DEL[5]   | SYNCSH_<br>DEL[4]   | SYNCSH_<br>DEL[3]   | SYNCSH_<br>DEL[2]   | SYNCSH_<br>DEL[1]   | 0x00    |

| LVDS_<br>REC_STAT1 | 0x19    | SMP_DEL [1]         | SMP_DEL<br>[0]      | N/A                 | N/A                 | SMP_FINE_<br>DEL[3] | SMP_FINE<br>_DEL[2] | SMP_FINE_<br>DEL[1] | SMP_FINE_<br>DEL[0] | 0xC7    |

| LVDS_<br>REC_STAT2 | 0x1A    | SMP_DEL<br>[9]      | SMP_DEL<br>[8]      | SMP_DEL<br>[7]      | SMP_DEL<br>[6]      | SMP_DEL<br>[5]      | SMP_DEL [4]         | SMP_DEL [3]         | SMP_DEL [2]         | 0x29    |

| LVDS_<br>REC_STAT3 | 0x1B    | DCI_DEL[1]          | DCI_DEL[0]          | N/A                 | N/A                 | SYNCOUT<br>PH[1]    | SYNCOUT<br>PH[0]    | CLKDIV<br>PH[1]     | CLKDIV<br>PH[0]     | 0xC0    |

| LVDS_<br>REC_STAT4 | 0x1C    | DCI_DEL[9]          | DCI_DEL[8]          | DCI_DEL[7]          | DCI_DEL[6]          | DCI_DEL[5]          | DCI_DEL[4]          | DCI_DEL[3]          | DCI_DEL[2]          | 0x29    |

| LVDS_<br>REC_STAT5 | 0x1D    | FINE_DEL_<br>PST[3] | FINE_DEL_<br>PST[2] | FINE_DEL_<br>PST[1] | FINE_DEL_<br>PST[0] | FINE_DEL_<br>PRE[3] | FINE_DEL_<br>PRE[2] | FINE_DEL_<br>PRE[1] | FINE_DEL_<br>PRE[0] | 0x86    |

| LVDS_<br>REC_STAT6 | 0x1E    | N/A                 | SYNCO_<br>DEL[6]    | SYNCO_<br>DEL[5]    | SYNCO_<br>DEL[4]    | SYNCO_<br>DEL[3]    | SYNCO_<br>DEL[2]    | SYNCO_<br>DEL[1]    | SYNCO_<br>DEL[0]    | 0x00    |

| Name               | Address | Bit 7              | Bit 6             | Bit 5              | Bit 4             | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Default |

|--------------------|---------|--------------------|-------------------|--------------------|-------------------|--------------------|--------------------|--------------------|--------------------|---------|

| LVDS_<br>REC_STAT7 | 0x1F    | SYNCSH_<br>DEL[0]  | N/A               | N/A                | N/A               | N/A                | N/A                | N/A                | N/A                | 0x00    |

| LVDS_<br>REC_STAT8 | 0x20    | SYNCSH_<br>DEL[8]  | SYNCSH_<br>DEL[7] | SYNCSH_<br>DEL[6]  | SYNCSH_<br>DEL[5] | SYNCSH_<br>DEL[4]  | SYNCSH_<br>DEL[3]  | SYNCSH_<br>DEL[2]  | SYNCSH_<br>DEL[1]  | 0x00    |

| LVDS_<br>REC_STAT9 | 0x21    | SYNC_TRK<br>_ON    | SYNC_INIT<br>_ON  | SYNC_LST<br>_LCK   | SYNC_LCK          | RCVR_TRK<br>_ON    | RCVR_FE_<br>ON     | RCVR_LST_<br>LCK   | RCVR_LCK           | 0x00    |

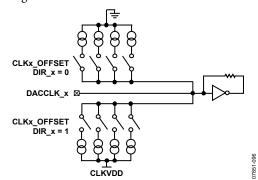

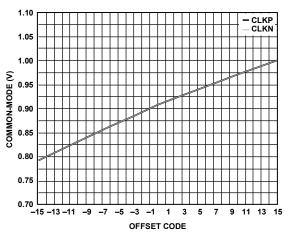

| CROSS_<br>CNT1     | 0x22    | N/A                | N/A               | N/A                | DIR_P             | CLKP_<br>OFFSET[3] | CLKP_<br>OFFSET[2] | CLKP_<br>OFFSET[1] | CLKP_<br>OFFSET[0] | 0x00    |

| CROSS_<br>CNT2     | 0x23    | N/A                | N/A               | N/A                | DIR_N             | CLKN_<br>OFFSET[3] | CLKN_<br>OFFSET[2] | CLKN_<br>OFFSET[1] | CLKN_<br>OFFSET[0] | 0x00    |

| PHS_DET            | 0x24    | N/A                | N/A               | PHS_DET<br>AUTO_EN | CMP_BST           | Bias[3]            | Bias[2]            | Bias[1]            | Bias[0]            | 0x00    |

| MU_DUTY            | 0x25    | MU_DUTY<br>AUTO_EN | POS/NEG           | ADJ[5]             | ADJ[4]            | ADJ[3]             | ADJ[2]             | ADJ[1]             | ADJ[0]             | 0x00    |

| MU_CNT1            | 0x26    | N/A                | Slope             | Mode[1]            | Mode[0]           | Read               | Gain[1]            | Gain[0]            | Enable             | 0x42    |

| MU_CNT2            | 0x27    | MUDEL[0]           | SrchMode<br>[1]   | SrchMode<br>[0]    | SetPhs[4]         | SetPhs[3]          | SetPhs[2]          | SetPhs[1]          | SetPhs[0]          | 0x40    |

| MU_CNT3            | 0x28    | MUDEL[8]           | MUDEL[7]          | MUDEL[6]           | MUDEL[5]          | MUDEL[4]           | MUDEL[3]           | MUDEL[2]           | MUDEL[1]           | 0x00    |

| MU_CNT4            | 0x29    | Search_Tol         | Retry             | ContRst            | Guard[4]          | Guard[3]           | Guard[2]           | Guard[1]           | Guard[0]           | 0x0B    |

| MU_STAT1           | 0x2A    | N/A                | N/A               | N/A                | N/A               | N/A                | N/A                | MU_LOST            | MU_LKD             | 0x00    |

| RSVD               | 0x2B    | N/A                | N/A               | N/A                | N/A               | N/A                | N/A                | N/A                | N/A                | N/A     |

| RSVD               | 0x2C    | N/A                | N/A               | N/A                | N/A               | N/A                | N/A                | N/A                | N/A                | N/A     |

| ANA_CNT1           | 0x32    | HDRM[7]            | HDRM[6]           | HDRM[5]            | HDRM[4]           | HDRM[3]            | HDRM[2]            | HDRM[1]            | HDRM[0]            | 0xCA    |

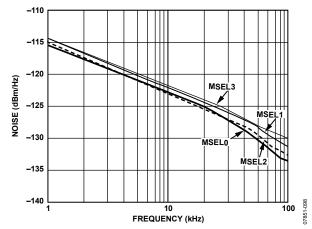

| ANA_CNT2           | 0x33    | N/A                | N/A               | N/A                | N/A               | N/A                | N/A                | MSEL[1]            | MSEL[0]            | 0x03    |

| RSVD               | 0x34    | N/A                | N/A               | N/A                | N/A               | N/A                | N/A                | N/A                | N/A                | N/A     |

| PART ID            | 0x35    | ID[7]              | ID[6]             | ID[5]              | ID[4]             | ID[3]              | ID[2]              | ID[1]              | ID[0]              | 0x40    |

#### **SPI REGISTERS**

Reading these registers returns previously written values for all defined register bits, unless otherwise noted.

#### Table 8. Mode Register (Register 0x00)

| Register<br>Name | Address <sup>1</sup> |    | Bit 7    | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------|----------------------|----|----------|---------|-------|-------|-------|-------|-------|-------|

| Mode             | 0x00                 | 00 | SDIO_DIR | LSB/MSB | Reset | N/A   | N/A   | N/A   | N/A   | N/A   |

<sup>&</sup>lt;sup>1</sup>The two-digit number is the decimal representation of the address.

#### **Table 9. Mode Register Bit Descriptions**

| Bit<br>Name | Read/Write | Description                                                                                                                                                                                                                                         | Reset Value for<br>Write Register |

|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| SDIO_DIR    | Read/write | 0: input only, per SPI standard. 1: bidirectional, per SPI standard.                                                                                                                                                                                | 0                                 |

| LSB/MSB     | Read/write | 0: MSB first, per SPI standard. 1: LSB first, per SPI standard. Change the LSB/MSB order in single-byte instructions only to avoid erratic behavior due to bit order errors.                                                                        | 0                                 |

| Reset       | Read/write | 0: default. Bit is in the inactive state. 1: all programmable bits return to their default state except Register 0x00, which is unaffected by the software reset. The software reset remains in effect until this bit is set to 0 (inactive state). | 0                                 |

#### Table 10. Power-Down Register (Register 0x01)

| Register   |       |                 |       |       |             |              |       |       |            |             |

|------------|-------|-----------------|-------|-------|-------------|--------------|-------|-------|------------|-------------|

| Name       | Addre | SS <sup>1</sup> | Bit 7 | Bit 6 | Bit 5       | Bit 4        | Bit 3 | Bit 2 | Bit 1      | Bit 0       |

| Power-Down | 0x01  | 01              | N/A   | N/A   | LVDS_DCO_PD | LVDS_RCVR_PD | N/A   | N/A   | CLK_REC_PD | DAC_BIAS_PD |

<sup>&</sup>lt;sup>1</sup>The two-digit number is the decimal representation of the address.

Table 11. Power-Down Register Bit Descriptions

| Bit Name     | Read/Write | Description                              | Reset Value for<br>Write Register |

|--------------|------------|------------------------------------------|-----------------------------------|

| LVDS_DCO_PD  | Read/write | 0: DCO enabled.                          | 0                                 |

|              |            | 1: DCO disabled.                         |                                   |

| LVDS_RCVR_PD | Read/write | 0: LVDS receiver enabled.                | 0                                 |

|              |            | 1: LSB receiver powered down.            |                                   |

| CLK_REC_PD   | Read/write | 0: internal clock receiver enabled.      | 0                                 |

|              |            | 1: internal clock receiver powered down. |                                   |

| DAC_BIAS_PD  | Read/write | 0: DAC bias circuitry enabled.           | 0                                 |

|              |            | 1: DAC bias circuitry powered down.      |                                   |

#### Table 12. Controller Clock Disable Register (Register 0x02)

| Register<br>Name | Addre | ess <sup>1</sup> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1       | Bit 0      |

|------------------|-------|------------------|-------|-------|-------|-------|-----------|-------|-------------|------------|

| CNT_CLK_Dis      | 0x02  | 02               | N/A   | N/A   | N/A   | N/A   | CLKGEN_PD | N/A   | REC_CNT_CLK | MU_CNT_CLK |

<sup>&</sup>lt;sup>1</sup>The two-digit number is the decimal representation of the address.

#### Table 13. Controller Clock Disable Register Bit Descriptions

| Bit Name    | Read/Write | Description                                    | Reset Value for<br>Write Register |

|-------------|------------|------------------------------------------------|-----------------------------------|

| CLKGEN_PD   | Read/write | 0: clocks enabled.                             | 0                                 |

|             |            | 1: clocks disabled.                            |                                   |

| REC_CNT_CLK | Read/write | 0: clock to LVDS receiver controller disabled. | 0                                 |

|             |            | 1: clock to LVDS receiver controller enabled.  |                                   |

| MU_CNT_CLK  | Read/write | 0: clock to mu controller disabled.            | 0                                 |

|             |            | 1: clock to mu controller enabled.             |                                   |

#### Table 14. IRQ Registers (Register 0x03, Register 0x04)

| Register<br>Name | Addre | ss¹ | Bit 7 | Bit 6 | Bit 5        | Bit 4        | Bit 3     | Bit 2     | Bit 1      | Bit 0      |

|------------------|-------|-----|-------|-------|--------------|--------------|-----------|-----------|------------|------------|

| IRQ_En           | 0x03  | 03  | N/A   | N/A   | SYNC_LST_EN  | SYNC_LCK_EN  | MULST_EN  | MULCK_EN  | RCV_LST_EN | RCV_LCK_EN |

| IRQ_Req          | 0x04  | 04  | N/A   | N/A   | SYNC_LST_IRQ | SYNC_LCK_IRQ | MULST_IRQ | MULCK_IRQ | RCVLST_IRQ | RCVLCK_IRQ |

<sup>&</sup>lt;sup>1</sup>The two-digit number is the decimal representation of the address.

#### **Table 15. IRQ Register Bit Descriptions**

| Bit Name     | Read/Write | Description                                                             | Reset Value for<br>Write Register |

|--------------|------------|-------------------------------------------------------------------------|-----------------------------------|

| SYNC_LST_EN  | Write      | 0: reset SYNC_LST_IRQ and disable future SYNC_LST_IRQ.                  | 0                                 |

|              |            | 1: enable SYNC_LST_IRQ request.                                         |                                   |

| SYNC_LCK_EN  | Write      | 0: reset SYNC_IRQ and disable future SYNC_LCK_IRQ.                      | 0                                 |

|              |            | 1: enable SYNC_IRQ request.                                             |                                   |

| MULST_EN     | Write      | 0: reset MULST_IRQ and disable future MULST_IRQ.                        | 0                                 |

|              |            | 1: enable MULST_IRQ request.                                            |                                   |

| MULCK_EN     | Write      | 0: reset MULCK_IRQ and disable future MULCK_IRQ.                        | 0                                 |

|              |            | 1: enable the MULCK_IRQ request.                                        |                                   |

| RCV_LST_EN   | Write      | 0: reset the RCVLST_IRQ and disable future RCVLST_IRQ.                  | 0                                 |

|              |            | 1: enable the RCVLST_IRQ request.                                       |                                   |

| RCV_LCK_EN   | Write      | 0: reset the RCV_IRQ interrupt and disable future MULCK_IRQ.            | 0                                 |

|              |            | 1: enable RCV_IRQ request.                                              |                                   |

| SYNC_LST_IRQ | Read       | 0: the sync controller has not lost lock.                               | 0                                 |

|              |            | 1: the sync controller has lost lock and an interrupt has occurred.     |                                   |

| SYNC_LCK_IRQ | Read       | 0: the sync controller is unlocked.                                     | 0                                 |

|              |            | 1: the sync controller has achieved lock and an interrupt has occurred. |                                   |

| MULST_IRQ    | Read       | 0: the mu controller has not lost lock.                                 | 0                                 |

|              |            | 1: the mu controller has lost lock and an interrupt has occurred.       |                                   |

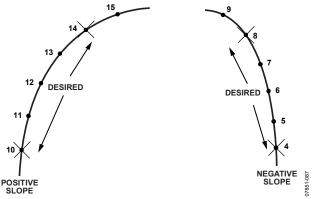

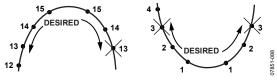

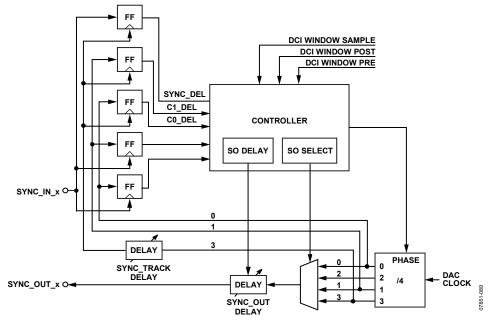

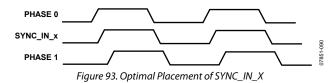

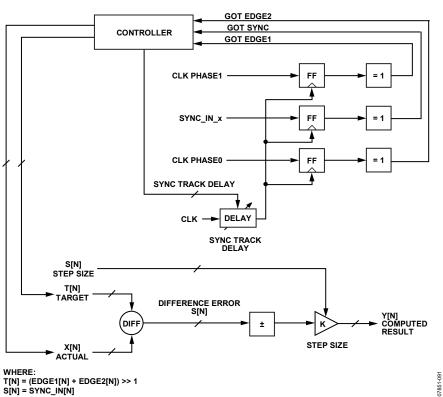

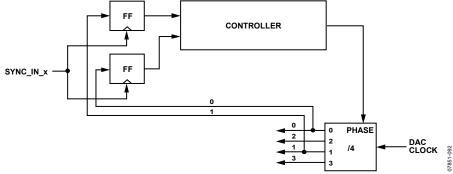

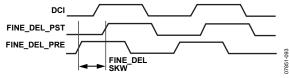

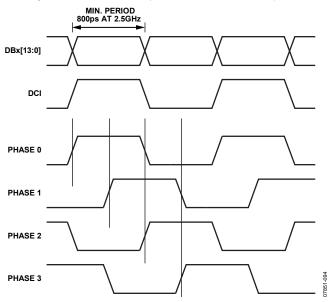

| Bit Name   | Read/Write | Description                                                            | Reset Value for<br>Write Register |