# <sup>2</sup>QUAD, 8-BIT, LOW-POWER, VOLTAGE OUTPUT, <sup>1</sup>C INTERFACE DIGITAL-TO-ANALOG CONVERTER

### FEATURES

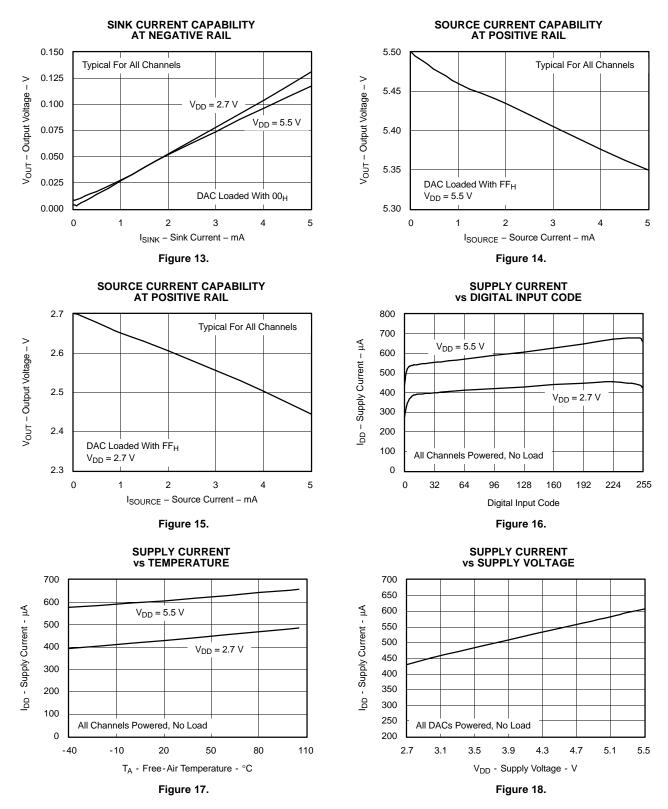

- Micropower Operation: 500 µA at 3 V V<sub>DD</sub>

- Fast Update Rate: 188 kSPS

- Power-On Reset to Zero

- 2.7-V to 5.5-V Analog Power Supply

- 8-Bit Monotonic

- I<sup>2</sup>C<sup>™</sup> Interface up to 3.4 Mbps

- Data Transmit Capability

- Rail-to-Rail Output Buffer Amplifier

- Double-Buffered Input Register

- Address Support for up to Sixteen DAC5573s

- Synchronous Update for up to 64 Channels

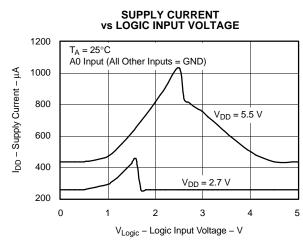

- Voltage Translators for all Digital Inputs

- Operation From –40°C to 105°C

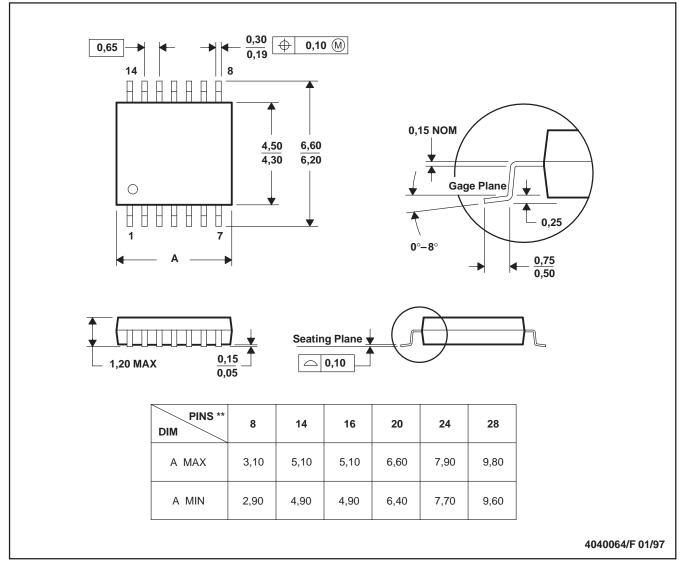

- Small 16 Lead TSSOP Package

### **APPLICATIONS**

- Process Control

- Data Acquisition Systems

- Closed-Loop Servo Control

- PC Peripherals

- Portable Instrumentation

## DESCRIPTION

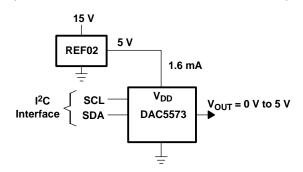

The DAC5573 is a low-power, quad channel, 8-bit buffered voltage output DAC. Its on-chip precision output amplifier allows rail-to-rail output swing. The DAC5573 utilizes an  $l^2$ C-compatible two-wire serial interface supporting high-speed interface mode with address support of up to sixteen DAC5573s for a total of 64 channels on the bus.

The DAC5573 requires an external reference voltage to set the output range of the DAC. The DAC5573 incorporates a power-on-reset circuit that ensures that the DAC output powers up at zero volts and remains there until a valid write takes place in the device. The DAC5573 contains a power-down feature, accessed via the internal control register, that reduces the current consumption of the device to 200 nA at 5 V.

The low power consumption of this part in normal operation makes it ideally suited to portable battery operated equipment. The power consumption is less than 3 mW at  $V_{DD}$  = 5 V reducing to 1  $\mu$ W in power-down mode.

The DAC5573 is available in a 16-lead TSSOP package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. I<sup>2</sup>C is a trademark of Philips Corporation.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

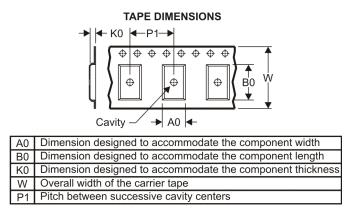

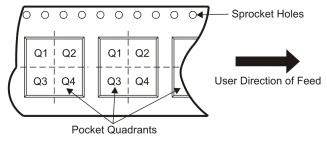

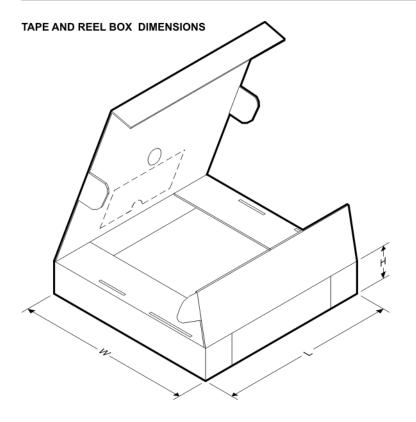

#### PACKAGE/ORDERING INFORMATION

| PRODUCT | PACKAGE  | PACKAGE<br>DRAWING<br>NUMBER | SPECIFICATION<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA          |

|---------|----------|------------------------------|---------------------------------------|--------------------|--------------------|--------------------------|

| DAC5573 | 16-TSSOP | PW                           | –40°C TO +105°C                       | D5573I             | DAC5573IPW         | 90 Piece Tube            |

|         |          |                              |                                       |                    | DAC5573IPWR        | 2000 Piece Tape and Reel |

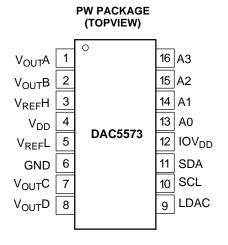

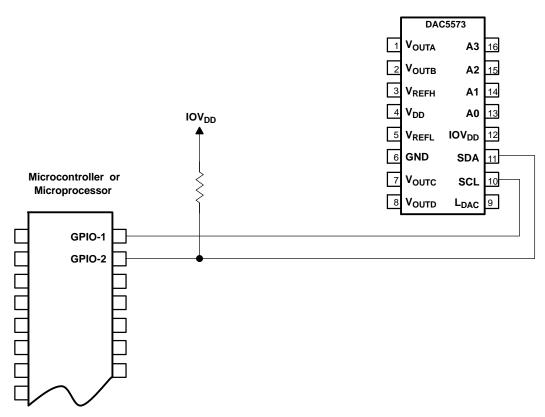

#### **PIN DESCRIPTIONS**

| PIN | NAME               | DESCRIPTION                                          |

|-----|--------------------|------------------------------------------------------|

| 1   | V <sub>OUT</sub> A | Analog output voltage from DAC A                     |

| 2   | V <sub>OUT</sub> B | Analog output voltage from DAC B                     |

| 3   | $V_{REF}H$         | Positive reference voltage input                     |

| 4   | $V_{DD}$           | Analog voltage supply input                          |

| 5   | $V_{REF}L$         | Negative reference voltage input                     |

| 6   | GND                | Ground reference point for all circuitry on the part |

| 7   | V <sub>OUT</sub> C | Analog output voltage from DAC C                     |

| 8   | V <sub>OUT</sub> D | Analog output voltage from DAC D                     |

| 9   | LDAC               | H/W synchronous V <sub>OUT</sub> update              |

| 10  | SCL                | Serial clock input                                   |

| 11  | SDA                | Serial data input                                    |

| 12  | $IOV_{DD}$         | I/O voltage supply input                             |

| 13  | A0                 | Device address select - I <sup>2</sup> C             |

| 14  | A1                 | Device address select - I <sup>2</sup> C             |

| 15  | A2                 | Device address select - Extended                     |

| 16  | A3                 | Device address select - Extended                     |

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| V <sub>DD</sub> to GND      |                                       | –0.3 V to +6 V                    |

|-----------------------------|---------------------------------------|-----------------------------------|

| Digital input voltage to GN | ND                                    | –0.3 V to V <sub>DD</sub> + 0.3 V |

| V <sub>OUT</sub> to GND     |                                       | –0.3 V to V <sub>DD</sub> + 0.3 V |

| Operating temperature ra    | nge                                   | –40°C to +105°C                   |

| Storage temperature rang    | e                                     | –65°C to +150°C                   |

| Junction temperature rang   | ge (T <sub>J</sub> max)               | +150°C                            |

| Power dissipation:          | Thermal impedance ( $R_{\Theta JA}$ ) | 161°C/W                           |

|                             | Thermal impedance ( $R_{\Theta JC}$ ) | 29°C/W                            |

| Lead temperature, solder    | ng: Vapor phase (60s)                 | 215°C                             |

| Power dissipation:          | Infrared (15s)                        | 220°C                             |

(1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = 2.7 V to 5.5 V,  $R_{L}$  = 2 k $\Omega$  to GND;  $C_{L}$  = 200 pF to GND; all specifications -40°C to +105°C, unless otherwise specified.

| PARAMETER                                                       | TEST CONDITIONS                                              | MIN                   | TYP    | MAX                   | UNITS         |

|-----------------------------------------------------------------|--------------------------------------------------------------|-----------------------|--------|-----------------------|---------------|

| STATIC PERFORMANCE <sup>(1)(2)</sup>                            |                                                              |                       |        |                       |               |

| Resolution                                                      |                                                              | 8                     |        |                       | Bits          |

| Relative accuracy                                               |                                                              |                       | ±0.25  | ±0.5                  | LSB           |

| Differential nonlinearity                                       | Specified monotonic by design                                |                       | ±0.1   | $\pm 0.25$            | LSB           |

| Zero-scale error                                                |                                                              |                       | 5      | 20                    | mV            |

| Full-scale error                                                |                                                              |                       | -0.15  | ±1.0                  | % of FSR      |

| Gain error                                                      |                                                              |                       |        | ±1.0                  | % of FSR      |

| Zero code error drift                                           |                                                              |                       | ±7     |                       | µV/∘C         |

| Gain temperature coefficient                                    |                                                              |                       | ± 3    |                       | ppm of FSR/°C |

| OUTPUT CHARACTERISTICS <sup>(3)</sup>                           |                                                              |                       |        |                       |               |

| Output voltage range                                            |                                                              | 0                     |        | V <sub>REF</sub> H    | V             |

| Output voltage settling time (full scale)                       | R <sub>L</sub> = ∞; 0 pF < C <sub>L</sub> < 200 pF           |                       | 6      | 8                     | μs            |

|                                                                 | $R_L = \infty$ ; $C_L = 500 \text{ pF}$                      |                       | 12     |                       | μs            |

| Slew rate                                                       |                                                              |                       | 1      |                       | V/µs          |

| dc crosstalk (channel-to-channel)                               |                                                              |                       | 0.0025 |                       | LSB           |

| ac crosstalk (channel-to-channel)                               | 1 kHz Sine Wave                                              |                       | -100   |                       | dB            |

| Capacitive load stability                                       | R <sub>L</sub> = ∞                                           |                       | 470    |                       | pF            |

|                                                                 | $R_L = 2 k\Omega$                                            |                       | 1000   |                       | pF            |

| Digital-to-analog glitch impulse                                | 1 LSB change around major<br>carry                           |                       | 12     |                       | nV-s          |

| Digital feedthrough                                             |                                                              |                       | 0.3    |                       | nV-s          |

| dc output impedance                                             |                                                              |                       | 1      |                       | Ω             |

| Short-circuit current                                           | V <sub>DD</sub> = 5 V                                        | 50                    |        |                       | mA            |

|                                                                 | V <sub>DD</sub> = 3 V                                        |                       | 20     |                       | mA            |

| Power-up time                                                   | Coming out of power-down<br>mode, V <sub>DD</sub> = +5 V     |                       | 2.5    |                       | μs            |

|                                                                 | Coming out of power-down<br>mode, V <sub>DD</sub> = +3 V     |                       | 5      |                       | μs            |

| REFERENCE INPUT                                                 | 1                                                            | l.                    |        |                       |               |

| V <sub>REF</sub> H Input range                                  |                                                              | 0                     |        | V <sub>DD</sub>       | V             |

| V <sub>REF</sub> L Input range                                  | V <sub>REF</sub> L <v<sub>REFH</v<sub>                       | 0                     | GND    | V <sub>DD</sub> /2    | V             |

| Reference input impedance                                       |                                                              |                       | 25     |                       | kΩ            |

| Reference current                                               | $V_{REF} = V_{DD} = +5 V$                                    |                       | 185    | 260                   | μA            |

|                                                                 | V <sub>REF</sub> =V <sub>DD</sub> = +3 V                     |                       | 122    | 200                   |               |

| LOGIC INPUTS <sup>(3)</sup>                                     |                                                              |                       |        |                       | I             |

| Input current                                                   |                                                              |                       |        | ±1                    | μA            |

| V <sub>IN L</sub> , Input low voltage                           |                                                              |                       |        | 0.3xIOV <sub>DD</sub> | V             |

| V <sub>IN H</sub> , Input high voltage                          |                                                              | 0.7xIOV <sub>DD</sub> |        |                       | V             |

| Pin Capacitance                                                 |                                                              |                       |        | 3                     | pF            |

| POWER REQUIREMENTS                                              | 1                                                            | <u>u</u>              |        |                       |               |

| V <sub>DD</sub> , IOV <sub>DD</sub>                             |                                                              | 2.7                   |        | 5.5                   | V             |

| I <sub>DD</sub> (normal operation), including reference current | Excluding load current                                       |                       |        |                       |               |

| I <sub>DD</sub> @ V <sub>DD</sub> =+3.6V to +5.5V               | V <sub>IH</sub> = IOV <sub>DD</sub> and V <sub>IL</sub> =GND |                       | 600    | 900                   | μA            |

| $I_{DD}$ @ $V_{DD}$ =+2.7V to +3.6V                             | $V_{IH}$ = IOV <sub>DD</sub> and $V_{IL}$ =GND               |                       | 500    | 750                   | μA            |

| I <sub>DD</sub> (all power-down modes)                          |                                                              |                       |        |                       |               |

Linearity tested using a reduced code range of 3 to 253; output unloaded.  $V_{REF}H = V_{DD}$  - 0.1,  $V_{REF}L = GND$ Specified by design and characterization, not production tested. (1)

(2) (3)

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{DD}$  = 2.7 V to 5.5 V,  $R_L$  = 2 k $\Omega$  to GND;  $C_L$  = 200 pF to GND; all specifications -40°C to +105°C, unless otherwise specified.

| PARAMETER                                         | TEST CONDITIONS                                | MIN | TYP  | MAX  | UNITS |

|---------------------------------------------------|------------------------------------------------|-----|------|------|-------|

| I <sub>DD</sub> @ V <sub>DD</sub> =+3.6V to +5.5V | $V_{IH}$ = IOV <sub>DD</sub> and $V_{IL}$ =GND |     | 0.2  | 1    | μA    |

| I <sub>DD</sub> @ V <sub>DD</sub> =+2.7V to +3.6V | $V_{IH}$ = IOV <sub>DD</sub> and $V_{IL}$ =GND |     | 0.05 | 1    | μA    |

| POWER EFFICIENCY                                  |                                                |     |      |      |       |

| I <sub>OUT</sub> /I <sub>DD</sub>                 | $I_{LOAD}$ = 2 mA, $V_{DD}$ = +5 V             |     | 93%  |      |       |

| TEMPERATURE RANGE                                 |                                                |     |      |      |       |

| Specified performance                             |                                                | -40 |      | +105 | °C    |

### TIMING CHARACTERISTICS

$V_{DD}$  = 2.7 V to 5.5 V,  $R_L$  = 2 k $\Omega$  to GND; all specifications –40°C to +105°C, unless otherwise specified.

| SYMBOL                             | PARAMETER                                                  | TEST CONDITIONS                                     | MIN                    | TYP N | IAX  | UNITS |

|------------------------------------|------------------------------------------------------------|-----------------------------------------------------|------------------------|-------|------|-------|

|                                    |                                                            | Standard mode                                       |                        |       | 100  | kHz   |

| f <sub>SCL</sub>                   |                                                            | Fast mode                                           |                        |       | 400  | kHz   |

|                                    | SCL clock frequency                                        | High-Speed mode, $C_B = 100 \text{ pF}$ max         |                        |       | 3.4  | MHz   |

|                                    |                                                            | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ |                        |       | 1.7  | MHz   |

|                                    | Bus free time between a STOP and                           | Standard mode                                       | 4.7                    |       |      | μs    |

| <sup>L</sup> BUF                   | START condition                                            | Fast mode                                           | 1.3                    |       |      | μs    |

|                                    |                                                            | Standard mode                                       | 4.0                    |       |      | μs    |

| t <sub>HD</sub> ; t <sub>STA</sub> | Hold time (repeated) START<br>condition                    | Fast mode                                           | 600                    |       |      | ns    |

|                                    |                                                            | High-speed mode                                     | 160                    |       |      | ns    |

|                                    |                                                            | Standard mode                                       | 4.7                    |       |      | μs    |

|                                    | LOW period of the COL clock                                | Fast mode                                           | 1.3                    |       |      | μs    |

| t <sub>LOW</sub>                   | LOW period of the SCL clock                                | High-speed mode, $C_B = 100 \text{ pF} \text{ max}$ | 160                    |       |      | ns    |

|                                    |                                                            | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ | 320                    |       |      | ns    |

|                                    |                                                            | Standard mode                                       | 4.0                    |       |      | μs    |

|                                    | LUCL paried of the SCL algely                              | Fast mode                                           | 600                    |       |      | ns    |

| t <sub>HIGH</sub>                  | HIGH period of the SCL clock                               | High-Speed Mode, C <sub>B</sub> = 100 pF max        | 60                     |       |      | ns    |

|                                    |                                                            | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ | 120                    |       |      | ns    |

|                                    |                                                            | Standard mode                                       | 4.7                    |       |      | μs    |

| t <sub>SU</sub> ; t <sub>STA</sub> | Setup time for a repeated START<br>condition               | Fast mode                                           | 600                    |       |      | ns    |

|                                    |                                                            | High-speed mode                                     | 160                    |       |      | ns    |

|                                    |                                                            | Standard mode                                       | 250                    |       |      | ns    |

| t <sub>SU</sub> ; t <sub>DAT</sub> | Data setup time                                            | Fast mode                                           | 100                    |       |      | ns    |

|                                    |                                                            | High-speed mode                                     | 10                     |       |      | ns    |

|                                    |                                                            | Standard mode                                       | 0                      | :     | 3.45 | μs    |

|                                    | Dete held firme                                            | Fast mode                                           | 0                      |       | 0.9  | μs    |

| t <sub>HD</sub> ; t <sub>DAT</sub> | Data hold time                                             | High-speed mode, $C_B = 100 \text{ pF} \text{ max}$ | 0                      |       | 70   | ns    |

|                                    |                                                            | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ | 0                      |       | 150  | ns    |

|                                    |                                                            | Standard mode                                       |                        | 1     | 000  | ns    |

|                                    |                                                            | Fast mode                                           | 20 + 0.1C <sub>B</sub> |       | 300  | ns    |

| t <sub>RCL</sub>                   | Rise time of SCL signal                                    | High-speed mode, C <sub>B</sub> = 100 pF max        | 10                     |       | 40   | ns    |

|                                    |                                                            | High-speed mode, $C_B = 400 \text{ pF}$ max         | 20                     |       | 80   | ns    |

|                                    |                                                            | Standard mode                                       |                        | 1     | 000  | ns    |

|                                    | Rise time of SCL signal after a                            | Fast mode                                           | 20 + 0.1C <sub>B</sub> |       | 300  | ns    |

| t <sub>RCL1</sub>                  | repeated START condition and after -<br>an acknowledge BIT | High-speed mode, C <sub>B</sub> = 100 pF max        | 10                     |       | 80   | ns    |

|                                    |                                                            | High-speed mode, $C_B = 400 \text{ pF}$ max         | 20                     |       | 160  | ns    |

# TIMING CHARACTERISTICS (continued)

$V_{DD}$  = 2.7 V to 5.5 V,  $R_L$  = 2 k $\Omega$  to GND; all specifications –40°C to +105°C, unless otherwise specified.

| SYMBOL                             | PARAMETER                          | TEST CONDITIONS                                     | MIN                    | TYP | MAX  | UNITS |

|------------------------------------|------------------------------------|-----------------------------------------------------|------------------------|-----|------|-------|

|                                    |                                    | Standard mode                                       |                        |     | 300  | ns    |

| 4                                  | Fall time of SCL signal            | Fast mode                                           | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

| t <sub>FCL</sub>                   |                                    | High-speed mode, $C_B = 100 \text{ pF} \text{ max}$ | 10                     |     | 40   | ns    |

|                                    |                                    | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ | 20                     |     | 80   | ns    |

|                                    |                                    | Standard mode                                       |                        |     | 1000 | ns    |

| +                                  | Piso time of SDA signal            | Fast mode                                           | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

| t <sub>RDA</sub>                   | Rise time of SDA signal            | High-speed mode, $C_B = 100 \text{ pF} \text{ max}$ | 10                     |     | 80   | ns    |

|                                    |                                    | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ | 20                     |     | 160  | ns    |

|                                    |                                    | Standard mode                                       |                        |     | 300  | ns    |

| •                                  | Fall time of SDA signal            | Fast mode                                           | 20 + 0.1C <sub>B</sub> |     | 300  | ns    |

| t <sub>FDA</sub>                   | Fail time of SDA signal            | High-speed mode, $C_B = 100 \text{ pF} \text{ max}$ | 10                     |     | 80   | ns    |

|                                    |                                    | High-speed mode, $C_B = 400 \text{ pF} \text{ max}$ | 20                     |     | 160  | ns    |

|                                    |                                    | Standard mode                                       | 4.0                    |     |      | μs    |

| t <sub>SU</sub> ; t <sub>STO</sub> | Setup time for STOP<br>condition   | Fast mode                                           | 600                    |     |      | ns    |

|                                    |                                    | High-speed mode                                     | 160                    |     |      | ns    |

| CB                                 | Capacitive load for SDA and SCL    |                                                     |                        |     | 400  | pF    |

| +                                  | Pulse width of spike               | Fast mode                                           |                        |     | 50   | ns    |

| t <sub>SP</sub>                    | suppressed                         | High-speed mode                                     |                        |     | 10   | ns    |

|                                    | Noise margin at the HIGH level for | Standard mode                                       |                        |     |      |       |

| V <sub>NH</sub>                    | each connected device              | Fast mode                                           | 0.2 V <sub>DD</sub>    |     |      | V     |

|                                    | (including hysteresis)             | High-speed mode                                     |                        |     |      |       |

|                                    | Noise margin at the LOW level for  | Standard mode                                       |                        |     |      |       |

| V <sub>NL</sub>                    | each connected device              | Fast mode                                           | 0.1 V <sub>DD</sub>    |     |      | V     |

|                                    | (including hysteresis)             | High-speed mode                                     |                        |     |      |       |

|                                    | 1                                  |                                                     | 1                      |     |      |       |

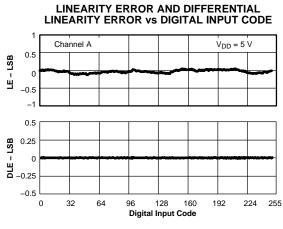

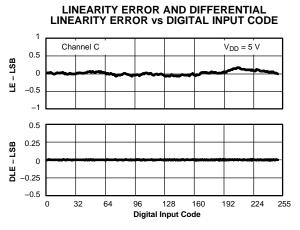

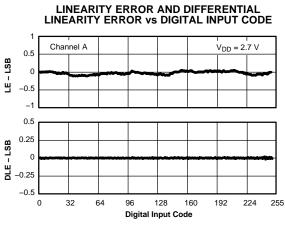

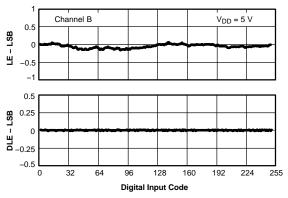

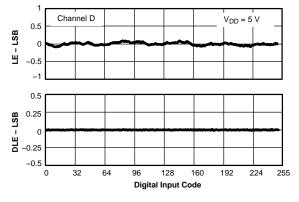

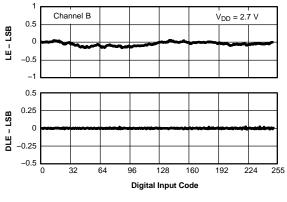

# TYPICAL CHARACTERISTICS

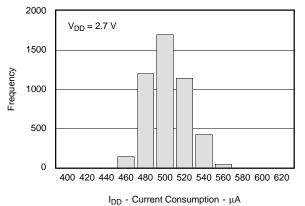

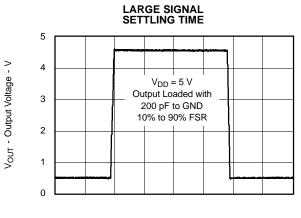

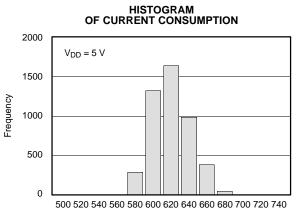

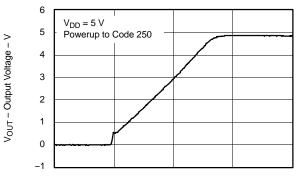

At  $T_A = +25^{\circ}C$ , unless otherwise noted.

#### Figure 1.

Figure 3.

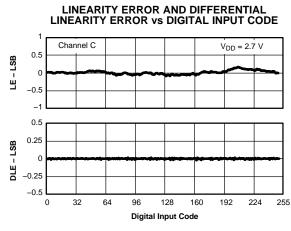

# LINEARITY ERROR AND DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE

#### Figure 2.

LINEARITY ERROR AND DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE

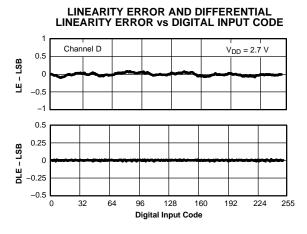

#### Figure 4.

#### LINEARITY ERROR AND DIFFERENTIAL LINEARITY ERROR vs DIGITAL INPUT CODE

Figure 6.

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , unless otherwise noted.

-0

TEXAS INSTRUMENTS www.ti.com

Figure 9.

Figure 11.

Figure 8.

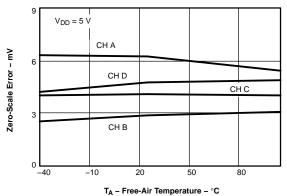

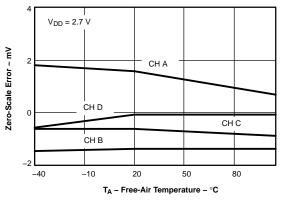

ZERO-SCALE ERROR vs TEMPERATURE

Figure 10.

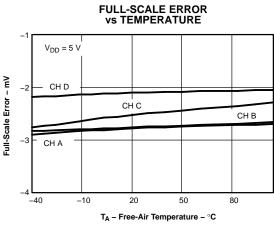

# FULL-SCALE ERROR vs TEMPERATURE

Figure 12.

SLAS401-NOVEMBER 2003

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , unless otherwise noted.

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , unless otherwise noted.

Ü

TEXAS INSTRUMENTS www.ti.com

Figure 21.

$I_{DD}$  - Current Consumption -  $\mu A$

EXITING POWER-DOWN MODE

Time (2 µs/div)

Figure 22.

Time (25 µs/div)

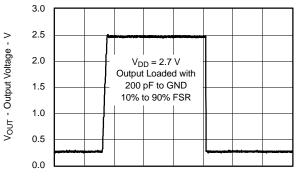

Figure 24.

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , unless otherwise noted.

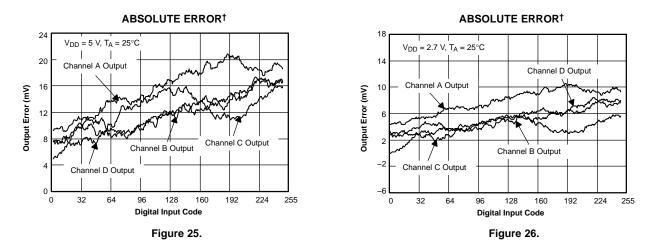

<sup>†</sup>Absolute error is the deviation from ideal DAC characteristics. It includes affects of offset, gain, and integral linearity.

# THEORY OF OPERATION

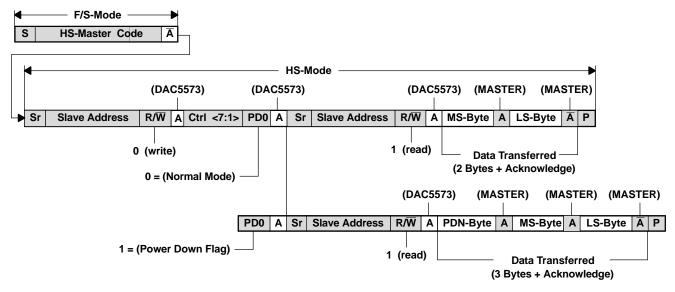

### **D/A SECTION**

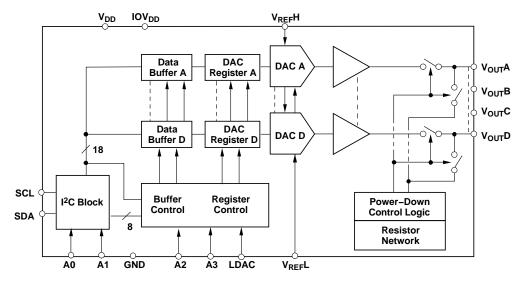

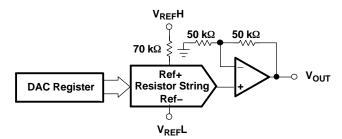

The architecture of the DAC5573 consists of a string DAC followed by an output buffer amplifier. Figure 27 shows a generalized block diagram of the DAC architecture.

Figure 27. R-String DAC Architecture

The input coding to the DAC5573 is unsigned binary, which gives the ideal output voltage as:

$$V_{OUT} = 2V_{REF}L + (V_{REF}H - V_{REF}L) \times \frac{D}{256}$$

Where D = decimal equivalent of the binary code that is loaded to the DAC register; it can range from 0 to 255.

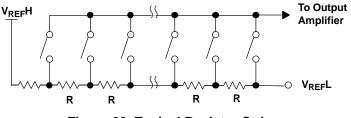

### **RESISTOR STRING**

The resistor string section is shown in Figure 28. It is basically a divide-by-2 resistor, followed by a string of resistors, each of value R. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier. Because the architecture consists of a string of resistors, it is specified monotonic.

Figure 28. Typical Resistor String

### **Output Amplifier**

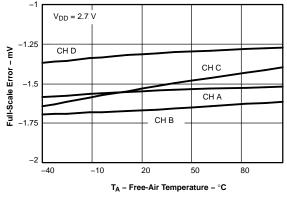

The output buffer is a gain-of-2 noninverting amplifier, capable of generating rail-to-rail voltages on its output, which gives an output range of 0V to  $V_{DD}$ . It is capable of driving a load of 2 k $\Omega$  in parallel with 1000 pF to GND. The source and sink capabilities of the output amplifier can be seen in the typical curves. The slew rate is 1 V/µs with a half-scale settling time of 8 µs with the output unloaded.

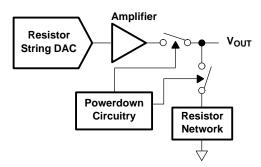

### I<sup>2</sup>C Interface

I<sup>2</sup>C is a 2-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000). The bus consists of a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is *idle*, both SDA and SCL lines are pulled high. All the I<sup>2</sup>C-compatible devices connect to the I<sup>2</sup>C bus through open drain I/O pins, SDA and SCL. A *master* device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A *slave* device receives and/or transmits data on the bus under control of the master device.

#### **THEORY OF OPERATION (continued)**

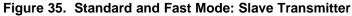

The DAC5573 works as a slave and supports the following data transfer modes, as defined in the I<sup>2</sup>C-Bus Specification: standard mode (100 kbps), fast mode (400 kbps), and high-speed mode (3.4 Mbps). The data transfer protocol for standard and fast modes is exactly the same, therefore they are referred to as F/S-mode in this document. The protocol for high-speed mode is different from the F/S-mode, and it is referred to as H/S-mode. The DAC5573 supports 7-bit addressing; 10-bit addressing and general call address are *not* supported.

#### **F/S-Mode Protocol**

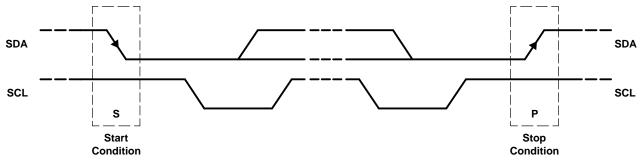

- The *master* initiates data transfer by generating a *start condition*. The *start condition* is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in Figure 29. All I<sup>2</sup>C-compatible devices recognize a *start condition*.

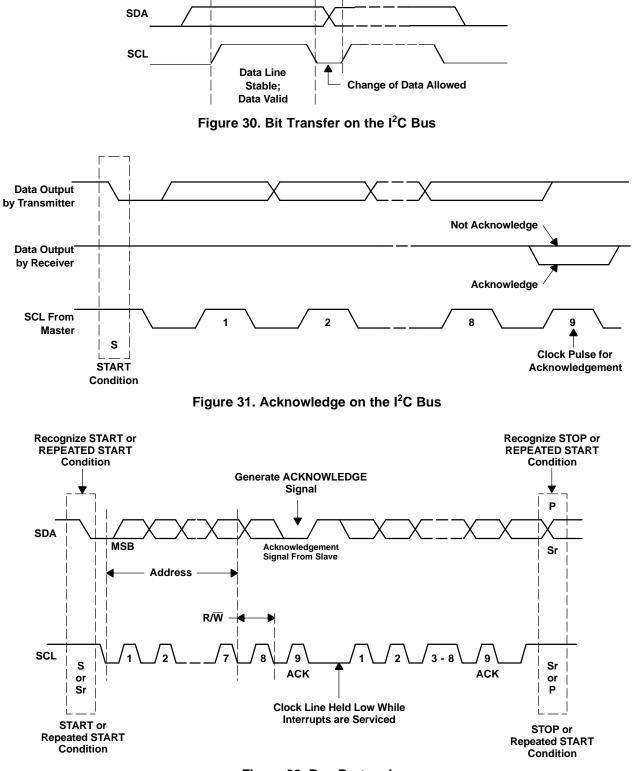

- The master then generates the SCL pulses, and transmits the 7-bit address and the *read/write direction bit* R/W on the SDA line. During all transmissions, the master ensures that data is *valid*. A *valid data* condition requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 30). All devices recognize the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a matching address generates an *acknowledge* (see Figure 31) by pulling the SDA line low during the entire high period of the ninth SCL cycle. Upon detecting this acknowledge, the master knows that communication link with a slave has been established.

- The master generates further SCL cycles to either *transmit* data to the slave (R/W bit 1) or *receive* data from the slave (R/W bit 0). In either case, the *receiver* must acknowledge the data sent by the *transmitter*. So an acknowledge signal can either be generated by the master or by the slave, depending on which one is the receiver. 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary.

- To signal the end of the data transfer, the master generates a *stop condition* by pulling the SDA line from low to high while the SCL line is high (see Figure 29). This releases the bus and stops the communication link with the addressed slave. All I<sup>2</sup>C-compatible devices must recognize the stop condition. Upon the receipt of a *stop condition*, all devices know that the bus is released, and they wait for a *start condition* followed by a matching address.

#### **H/S-Mode Protocol**

- When the bus is idle, both SDA and SCL lines are pulled high by the pullup devices.

- The master generates a start condition followed by a valid serial byte containing H/S master code 00001XXX. This transmission is made in F/S mode at no more than 400 Kbps. No device is allowed to acknowledge the H/S master code, but all devices must recognize it and switch their internal setting to support 3.4 Mbps operation.

- The master then generates a repeated start condition (a repeated start condition has the same timing as the start condition). After this repeated start condition, the protocol is the same as F/S-mode, except that transmission speeds up to 3.4 Mbps are allowed. A stop condition ends the H/S-mode and switches all the internal settings of the slave devices to support the F/S-mode. Instead of using a stop condition, repeated start conditions must be used to secure the bus in H/S-mode.

Figure 29. START and STOP Conditions

#### **THEORY OF OPERATION (continued)**

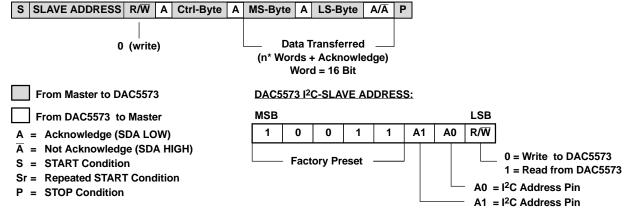

Figure 32. Bus Protocol

#### DAC5573 I<sup>2</sup>C Update Sequence

TEXAS INSTRUMENTS www.ti.com

The DAC5573 requires a start condition, a valid I<sup>2</sup>C address, a control byte, an MSB byte, and an LSB byte for a single update. After the receipt of each byte, DAC5573 acknowledges by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the DAC5573. The control byte sets the operational mode of the selected DAC5573. Once the operational mode is selected by the control byte, DAC5573 expects an MSB byte followed by an LSB byte for data update to occur. DAC5573 performs an update on the falling edge of the acknowledge signal that follows the LSB byte.

The control byte needs not to be resent until a change in operational mode is required. The bits of the control byte continuously determine the type of update performed. Thus, for the first update, DAC5573 requires a start condition, a valid I<sup>2</sup>C address, a control byte, an MSB byte and an LSB byte. For all consecutive updates, DAC5573 needs an MSB byte, and an LSB byte as long as the control command remains the same. MSB byte contains DAC data LSB byte contains 8 *don't care* bits.

Using the I<sup>2</sup>C high-speed mode ( $f_{scl}$ = 3.4 MHz), the clock running at 3.4 MHz, each 8-bit DAC update other than the first update can be done within 18 clock cycles (MSB byte, acknowledge signal, LSB byte, acknowledge signal), at 188.88 kSPS. Using the fast mode ( $f_{scl}$ = 400 kHz), clock running at 400 kHz, maximum DAC update rate is limited to 22.22 kSPS. Once a stop condition is received, DAC5573 releases the I<sup>2</sup>C bus and awaits a new start condition.

#### Address Byte

| MSB |   |   |   |   |    |    | LSB |

|-----|---|---|---|---|----|----|-----|

| 1   | 0 | 0 | 1 | 1 | A1 | A0 | R/W |

The address byte is the first byte received following the START condition from the master device. The first five bits (MSBs) of the address are factory preset to 10011. The next two bits of the address are the device select bits A1 and A0. The A1, A0 address inputs can be connected to  $V_{DD}$  or digital GND, or can be actively driven by TTL/CMOS logic levels. The device address is set by the state of these pins during the power-up sequence of the DAC5573. Up to 16 devices (DAC5573) can still be connected to the same I<sup>2</sup>C-bus.

#### **Broadcast Address Byte**

| MSB |   |   |   |   |   |   | LSB |

|-----|---|---|---|---|---|---|-----|

| 1   | 0 | 0 | 1 | 0 | 0 | 0 | 0   |

Broadcast addressing is also supported by DAC5573. Broadcast addressing can be used for synchronously updating or powering down multiple DAC5573 devices. DAC5573 is designed to work with other members of the DAC857x and DAC757x families to support multichannel synchronous update. Using the broadcast address, DAC5573 responds regardless of the states of the address pins. Broadcast is supported only in write mode (master writes to DAC5573).

#### TEXAS INSTRUMENTS www.ti.com

### **Control Byte**

| MSB |    |    |    |   |      |      | LSB |

|-----|----|----|----|---|------|------|-----|

| A3  | A2 | L1 | L0 | Х | Sel1 | Sel0 | PD0 |

## Table 1. Control Register Bit Descriptions

| Bit Name | Bit Number/De           | Bit Number/Description                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A3       | Extended addr           | ess bit                                                                                                                                                                                                                                                                                                                                         | The state of these bits must match the state of pins A3 and A2 in order for a proper                                                                                                                                                                                                                           |  |  |  |  |  |

| A2       | Extended addr           | ess bit                                                                                                                                                                                                                                                                                                                                         | DAC5573 data update, except in broadcast update mode.                                                                                                                                                                                                                                                          |  |  |  |  |  |

| L1       | Load1 (mode s           | select) bit                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| L2       | Load0 (mode select) bit |                                                                                                                                                                                                                                                                                                                                                 | Are used for selecting the update mode.                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|          | 00                      |                                                                                                                                                                                                                                                                                                                                                 | a. The contents of MS-BYTE and LS-BYTE (or power down information) are stored in the<br>gister of a selected channel. This mode does not change the DAC output of the selected                                                                                                                                 |  |  |  |  |  |

|          | 01                      | LS-BYTE (or                                                                                                                                                                                                                                                                                                                                     | Update selected DAC with I <sup>2</sup> C data. Most commonly utilized mode. The contents of MS-BYTE and LS-BYTE (or power down information) are stored in the temporary register and in the DAC register of the selected channel. This mode changes the DAC output of the selected channel with the new data. |  |  |  |  |  |

|          | 10                      | 4-channel synchronous update. The contents of MS-BYTE and LS-BYTE (or power down information) are stored in the temporary register and in the DAC register of the selected channel. Simultaneously, the other three channels get updated with previously stored data from the temporary register. This mode updates all four channels together. |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | 11                      | regardless of                                                                                                                                                                                                                                                                                                                                   | date mode. This mode has two functions. In broadcast mode, DAC5573 responds local address matching, and channel selection becomes irrelevant as all channels update. intended to enable up to 64 channels simultaneous update, if used with the I <sup>2</sup> C broadcast 1 0000).                            |  |  |  |  |  |

|          |                         | If Sel1=0                                                                                                                                                                                                                                                                                                                                       | All four channels are updated with the contents of their temporary register data.                                                                                                                                                                                                                              |  |  |  |  |  |

|          |                         | If Sel1=1                                                                                                                                                                                                                                                                                                                                       | All four channels are updated with the MS-BYTE and LS-BYTE data or powerdown.                                                                                                                                                                                                                                  |  |  |  |  |  |

| Sel1     | Buff Sel1 Bit           | ι.                                                                                                                                                                                                                                                                                                                                              | Channel select bits                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Sel0     | Buff Sel0 Bit           |                                                                                                                                                                                                                                                                                                                                                 | Channel select bits                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|          | 00                      | Channel A                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | 01                      | Channel B                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | 10                      | Channel C                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | 11                      | Channel D                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| PD0      | Power Down F            | lag                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | 0                       | Normal opera                                                                                                                                                                                                                                                                                                                                    | tion                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|          | 1 Power-down            |                                                                                                                                                                                                                                                                                                                                                 | ilag (MSB7 and MSB6 indicate a power-down operation, as shown in Table 2).                                                                                                                                                                                                                                     |  |  |  |  |  |

| SLAS401-NOVEMBER 200 | าว |

|----------------------|----|

|                      | 55 |

| Table 2. Control Byte                               |                               |       |           |               |              |            |           |               |                |                                                     |                                                                    |

|-----------------------------------------------------|-------------------------------|-------|-----------|---------------|--------------|------------|-----------|---------------|----------------|-----------------------------------------------------|--------------------------------------------------------------------|

| C7                                                  | C6                            | C5    | C4        | C3            | C2           | C1         | C0        | MSB7          | MSB6           | MSB5                                                |                                                                    |

| A3                                                  | A2                            | Load1 | Load0     | Don't<br>Care | Ch Sel 1     | Ch Sel 0   | PD0       | MSB<br>(PD1)  | MSB-1<br>(PD2) | MSB-2LSB                                            | DESCRIPTION                                                        |

|                                                     | lress<br>ect)                 |       |           |               |              |            |           |               |                |                                                     |                                                                    |

| should<br>spond                                     | nd A2<br>I corre-<br>I to the | 0     | 0         | х             | 0            | 0          | 0         |               | Dat            | a                                                   | Write to temporary register A (TRA) with data                      |

| package ad-<br>dress, set via<br>pins A3 and<br>A2) |                               | 0     | 0         | x             | 0            | 1          | 0         |               | Dat            | а                                                   | Write to temporary register B (TRB) with data                      |

|                                                     | _)                            | 0     | 0         | x             | 1 0 0 Data   |            |           |               |                |                                                     | Write to temporary register C (TRC) with data                      |

|                                                     |                               | 0     | 0         | x             | 1            | 1 1 0 Data |           |               |                | Write to temporary<br>register D (TRD) with<br>data |                                                                    |

|                                                     |                               | 0     | 0         | x             | (00, 01, 10, | , or 11)   | 1         | See T         | able 8         | 0                                                   | Write to TRx (selected<br>by C2 &C1<br>w/Powerdown Command         |

|                                                     |                               | 0     | 1         | x             | (00, 01, 10, | , or 11)   | 0         | Data          |                |                                                     | Write to TRx (selected<br>by C2 &C1 and load<br>DACx w/data        |

|                                                     |                               | 0     | 1         | х             | (00, 01, 10, | , or 11)   | 1         | See T         | able 8         | 0                                                   | Power-down DACx<br>(selected by C2 and C1)                         |

|                                                     |                               | 1     | 0         | x             | (00, 01, 10, | , or 11)   | 0         |               | Dat            | a                                                   | Write to TRx (selected<br>by C2 &C1 w/ data and<br>load all DACs   |

|                                                     |                               | 1     | 0         | x             | (00, 01, 10, | , or 11)   | 1         | See Table 8 0 |                |                                                     | Power-down DACx<br>(selected by C2 and C1)<br>& load all DACs      |

|                                                     |                               | Bro   | oadcast M | odes (co      | ntrols up to | 4 devices  | on a sing | le serial b   | us)            |                                                     |                                                                    |

| х                                                   | х                             | 1     | 1         | x             | 0            | х          | х         | ×             |                |                                                     | Update all DACs, all devices with previously stored TRx data       |

| х                                                   | х                             | 1     | 1         | x             | 1            | х          | 0         | Data          |                |                                                     | Update all DACs, all<br>devices with MSB[7:0]<br>and LSB[7:0] data |

| х                                                   | х                             | 1     | 1         | х             | 1            | х          | 1         | See Table 8 0 |                |                                                     | Power-down all DACs, all devices                                   |

#### Most Significant Byte

Most significant byte MSB[7:0] consists of eight most significant bits of 8-bit unsigned binary D/A conversion data. C0=1, MSB[7], MSB[6] indicate a power-down operation as shown in Table 8.

#### Least Significant Byte

Least significant byte LSB[7:0] consists of the 8 *don't care* bits. DAC5573 updates at the falling edge of the acknowledge signal that follows the LSB[0] bit. Therefore, the LS byte is needed for the update to occur.

#### **Default Readback Condition**

If the user initiates a readback of a specified channel without first writing data to that specified channel, the default readback is all zeros, since the readback register is initialized to 0 during the power on reset phase.

#### LDAC Functionality

Depending on the control byte, DACs are synchronously updated on the falling edge of the acknowledge signal that follows LS byte. The LDAC pin is required only when an external timing signal is used to update all the channels of the DAC asynchronously. LDAC is a positive edge triggered asynchronous input that allows four DAC output voltages to be updated simultaneously with temporary register data. The LDAC trigger should only be used after the buffer's temporary registers are properly updated through software.

#### DAC5573 Registers

| REGISTER                                  | DESCRIPTION                                                                                                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTRL[7:0]                                 | Stores 8-bit wide control byte sent by the master                                                                                                                           |

| MSB[7:0]                                  | Stores the 8 most significant bits of unsigned binary data sent by the master. Can also store 2-bit power-down data.                                                        |

| TRA[9:0], TRB[9:0],<br>TRC[9:0], TRD[9:0] | 10-bit temporary storage registers assigned to each channel. Two MSBs store power-down information, 8 LSBs store data.                                                      |

| DRA[9:0], DRB[9:0],<br>DRC[9:0], DRD[9:0] | 10-bit DAC registers for each channel. Two MSBs store power-down information, 8 LSBs store DAC data. An update of this register means a DAC update with data or power down. |

#### Table 3. DAC5573 Architecture Register Descriptions

#### DAC5573 as a Slave Receiver—Standard and Fast Mode

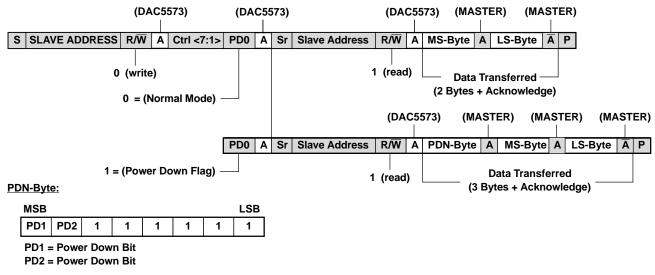

Figure 33 shows the standard and fast mode master transmitter addressing a DAC5573 *Slave Receiver* with a 7-bit address.

Figure 33. Standard and Fast Mode: Slave Receiver

### DAC5573 as a Slave Receiver—High-Speed Mode

Figure 34 shows the high-speed mode master transmitter addressing a DAC5573 *Slave Receiver* with a 7-bit address.

| <            | — F/S        | -Mode  | ) —   |          | <        |      |       |      |            |    | HS-Mod    | е —          |                     |                   |              |                                  |      | -   | - F/S-Mode    |

|--------------|--------------|--------|-------|----------|----------|------|-------|------|------------|----|-----------|--------------|---------------------|-------------------|--------------|----------------------------------|------|-----|---------------|

| S            | HS-Ma        | ster C | ode   | Ā        | Sr       | Slav | e Add | ress | R/W        | Α  | Ctrl-Byte | e A          | MS-B                | Syte              | AI           | LS-Byte                          | A/A  | Ρ   |               |

| <u>HS-</u> I | Mode M       | aster  | Code: |          |          |      |       | 0    | <br>(write | e) |           |              | (n*                 | Word              | s + /        | ansferred<br>Acknowl<br>= 16 Bit | -    | 4   | Mode Continue |

| MSE          | 3            |        |       |          |          |      |       | LSB  |            |    |           |              |                     |                   |              |                                  |      |     |               |

| 0            | 0            | 0      | 0     | 1        |          | X    | Х     | R/W  |            |    | Contro    | I Byt        | <u>e:</u>           |                   |              |                                  |      |     |               |

|              |              |        |       |          |          |      |       |      | •          |    | MSB       |              |                     |                   |              |                                  |      | LSB | _             |

| <u>MS-</u>   | Byte:        |        |       |          |          |      |       |      |            |    | A3        | A2           | L1                  | L0                | X            |                                  | Sel2 | PD0 | ]             |

| MSE          | 3            |        |       |          |          |      |       | LSB  |            |    | 710       |              | tende               |                   |              |                                  |      |     |               |

| D7           | D6           | D5     | D4    | D        | 3        | D2   | D1    | D0   | ]          |    |           |              | tende<br>ad1 (N     |                   |              |                                  |      |     |               |

| LS-I         | <u>Byte:</u> | •      |       | 1        | I        |      |       | LSB  | J          |    | L0        | = Lo<br>= Bi | oad0 (N<br>uff Sel1 | /lode :<br>1 (Cha | Sele<br>anne |                                  |      |     |               |

| X            | x            | x      | x     | X        | <u> </u> | х    | х     | X    | 1          |    |           |              | ower D              | •                 |              | ,                                | ы    |     |               |

| D11          | – D0 = I     | Data B | its   | <u> </u> |          |      |       | 1    | J          |    | X = D     | on't         | Care                |                   | -            |                                  |      |     |               |

Figure 34. High-Speed Mode: Slave Receiver

#### Master Transmitter Writing to a Slave Receiver (DAC5573) in Standard/Fast Modes

All write access sequences begin with the device address (with R/W = 0) followed by the control byte. This control byte specifies the operation mode of DAC5573 and determines which channel of DAC5573 is being accessed in the subsequent read/write operation. The LSB of the control byte (PD0-Bit) determines whether the following data is power-down data or regular data.

With (PD0-Bit = 0) the DAC5573 expects to receive data in the following sequence HIGH-BYTE - LOW-BYTE - HIGH-BYTE - LOW-BYTE..., until a STOP Condition or REPEATED START Condition on the I<sup>2</sup>C bus is recognized (refer to the DATA INPUT MODE section of Table 4).

With (PD0-Bit = 1) the DAC5573 expects to receive 2 bytes of power-down data (refer to the POWER DOWN MODE section of Table 4).

| DATA INPUT N | IODE                                       |                      |                             |                      |          |            |            |     |                              |  |  |  |

|--------------|--------------------------------------------|----------------------|-----------------------------|----------------------|----------|------------|------------|-----|------------------------------|--|--|--|

| Transmitter  | MSB                                        | 6                    | 5                           | 4                    | 3        | 2          | 1          | LSB | Comment                      |  |  |  |

| Master       |                                            |                      | 1                           | \$                   | Start    | 1          | 1          |     | Begin sequence               |  |  |  |

| Master       | 1                                          | 0                    | 0                           | 1                    | 1        | A1         | A0         | R/W | Write addressing (R/W=0)     |  |  |  |

| DAC5573      | DAC5573 Acknowledges                       |                      |                             |                      |          |            |            |     |                              |  |  |  |

| Master       | A3                                         | A2                   | Load 1                      | Load 0               | х        | Buff Sel 1 | Buff Sel 0 | PD0 | Control byte (PD0=0)         |  |  |  |

| DAC5573      |                                            |                      |                             | DAC5573              | Acknowle | edges      |            |     |                              |  |  |  |

| Master       | D7                                         | D6                   | D5                          | D4                   | D3       | D2         | D1         | D0  | Writing data word, high byte |  |  |  |

| DAC5573      |                                            |                      |                             | DAC5573              | Acknowle | edges      |            |     |                              |  |  |  |

| Master       | х                                          | х                    | х                           | х                    | х        | х          | х          | х   | Writing data word, low byte  |  |  |  |

| DAC5573      |                                            | DAC5573 Acknowledges |                             |                      |          |            |            |     |                              |  |  |  |

| Master       |                                            |                      | Data or done <sup>(2)</sup> |                      |          |            |            |     |                              |  |  |  |

| POWER DOWN   | MODE                                       |                      |                             |                      |          |            |            |     |                              |  |  |  |

| Transmitter  | MSB                                        | 6                    | 5                           | 4                    | 3        | 2          | 1          | LSB | Comment                      |  |  |  |

| Master       |                                            |                      |                             | ;                    | Start    |            |            |     | Begin sequence               |  |  |  |

| Master       | 1                                          | 0                    | 0                           | 1 1 A1 A0 <b>R</b> / |          |            |            | R/W | Write addressing (R/W=0)     |  |  |  |

| DAC5573      |                                            |                      |                             | DAC5573              | Acknowle | edges      |            |     |                              |  |  |  |

| Master       | A3                                         | A2                   | Load 1                      | Load 0               | х        | Buff Sel 1 | Buff Sel 0 | PD0 | Control byte (PD0 = 1)       |  |  |  |

| DAC5573      |                                            |                      |                             | DAC5573              | Acknowle | edges      |            |     |                              |  |  |  |

| Master       | PD1                                        | PD2                  | 0                           | 0                    | 0        | 0          | 0          | 0   | Writing data word, high byte |  |  |  |

| DAC5573      | DAC5573 Acknowledges                       |                      |                             |                      |          |            |            |     |                              |  |  |  |

| Master       | х                                          | х                    | х                           | х                    | х        | х          | х          | х   | Writing data word, low byte  |  |  |  |

| DAC5573      |                                            |                      |                             | DAC5573              | Acknowle | edges      |            |     |                              |  |  |  |

| Master       | Stop or Repeated Start <sup>(1)</sup> Done |                      |                             |                      |          |            |            |     |                              |  |  |  |

#### Table 4. Write Sequence in F/S Mode

(1) Use repeated START to secure bus operation and loop back to the stage of write addressing for next Write.

(2) Once DAC5573 is properly addressed and control byte is sent, HIGH-BYTE-LOW-BYTE sequences can repeat until a STOP condition or repeated START condition is received.

# TEXAS INSTRUMENTS www.ti.com

#### Master Transmitter Writing to a Slave Receiver (DAC5573) in HS Mode

When writing data to the DAC5573 in HS-mode, the master begins to transmit what is called the *HS-Master Code* (0000 1XXX) in F/S-mode. No device is allowed to acknowledge the *HS-Master Code*, so the *HS-Master Code* is followed by a NOT acknowledge.

The master then *switches* to HS-mode and issues a *repeated start* condition, followed by the address byte (with R/W = 0) after which the DAC5573 acknowledges by pulling SDA low. This address byte is usually followed by the control byte, which is also acknowledged by the DAC5573. The LSB of the control byte (PD0-Bit) determines if the following data is *power-down data* or regular data.

With (PD0-Bit = 0) the DAC5573 expects to receive data in the following sequence HIGH-BYTE – LOW-BYTE – HIGH-BYTE – LOW-BYTE..., until a STOP condition or *repeated start* condition on the  $I^2C$  bus is recognized (refer to Table 5 HS-MODE WRITE SEQUENCE - DATA).

With (PD0-Bit = 1) the DAC5573 expects to receive 2 bytes of power-down data (refer to Table 5 HS-MODE WRITE SEQUENCE - POWER DOWN).

| HS MODE WR  | ITE SEQUI            | ENCE - I                                   | DATA                        |         |           |            |            |     |                                               |  |  |  |  |

|-------------|----------------------|--------------------------------------------|-----------------------------|---------|-----------|------------|------------|-----|-----------------------------------------------|--|--|--|--|

| Transmitter | MSB                  | 6                                          | 5                           | 4       | 3         | 2          | 1          | LSB | Comment                                       |  |  |  |  |

| Master      |                      |                                            |                             | S       | Start     |            |            |     | Begin sequence                                |  |  |  |  |

| Master      | 0                    | 0                                          | 0                           | 0       | 1         | Х          | Х          | Х   | HS mode master code                           |  |  |  |  |

| NONE        |                      |                                            |                             | Not acl | knowled   | ge         |            |     | No device may acknowledge HS mas-<br>ter code |  |  |  |  |

| Master      |                      |                                            |                             | Repe    | ated star | t          |            |     |                                               |  |  |  |  |

| Master      | 1                    | 0                                          | 0                           | 1       | 1         | A1         | A0         | R/W | Write addressing ( <b>R/W=0</b> )             |  |  |  |  |

| DAC5573     |                      |                                            |                             | DAC5573 | acknowle  | edges      |            |     |                                               |  |  |  |  |

| Master      | 0                    | 0                                          | Load 1                      | Load 0  | 0         | Buff Sel 1 | Buff Sel 0 | PD0 | Control byte (PD0=0)                          |  |  |  |  |

| DAC5573     |                      | DAC5573 acknowledges                       |                             |         |           |            |            |     |                                               |  |  |  |  |

| Master      | D7                   | D6                                         | D5                          | D4      | D3        | D2         | D1         | D0  | Writing data word, MSB                        |  |  |  |  |

| DAC5573     | DAC5573 acknowledges |                                            |                             |         |           |            |            |     |                                               |  |  |  |  |

| Master      | х                    | х                                          | х                           | х       | х         | х          | х          | х   | Writing data word, LSB                        |  |  |  |  |