SRAM

Статическая память с произвольным доступом (SRAM, static random access memory) — полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в динамической памяти (DRAM*). Тем не менее, сохранять данные без перезаписи SRAM может, только пока есть питание, то есть SRAM остается энергозависимым типом памяти. Произвольный доступ (RAM* — random access memory) — возможность выбирать для записи/чтения любой из битов (тритов) (чаще байтов (трайтов), зависит от особенностей конструкции), в отличие от памяти с последовательным доступом (SAM, англ. sequential access memory).

Двоичная SRAM

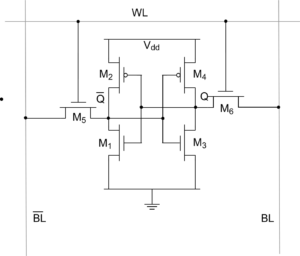

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрёстно (кольцом) включённых инверторов и ключевых транзисторов для обеспечения доступа к ячейке. Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы. Недостатком такого решения является рост статического энергопотребления.

Линия WL (Word Line) управляет двумя транзисторами доступа. Линии BL и BL (Bit Line) — битовые линии, используются и для записи данных, и для чтения данных.

Запись. При подаче «0» на линию BL или BL параллельно включенные транзисторные пары (M5 и M1) и (M6 и M3) образуют логические схемы 2ИЛИ, последующая подача «1» на линию WL открывает транзистор M5 или M6, что приводит к соответствующему переключению триггера.

Чтение. При подаче «1» на линию WL открываются транзисторы M5 и M6, уровни, записанные в триггере, выставляются на линии BL и BL и попадают на схемы чтения.

Восьмитранзисторная ячейка двоичной SRAM описана в.

Переключение триггеров через транзисторы доступа является неявной логической функцией приоритетного переключения, которая в явном виде, для двоичных триггеров, строится на двухвходовых логических элементах 2ИЛИ-НЕ или 2И-НЕ. Схема ячейки с явным переключением является обычным RS-триггером. При явной схеме переключения линии чтения и записи разделяются, отпадает нужда в транзисторах доступа в схеме записи-чтения с неявным приоритетом (по 2 транзистора на 1 ячейку), но появляется нужда в схемах записи-чтения с явным приоритетом.

В настоящее время появилась усовершенствованная схема с обратной связью, отключаемой сигналом записи, которая не требует транзисторов нагрузки и соответственно избавлена от высокого потребления энергии при записи.

Добавить комментарий

Для отправки комментария вам необходимо авторизоваться.